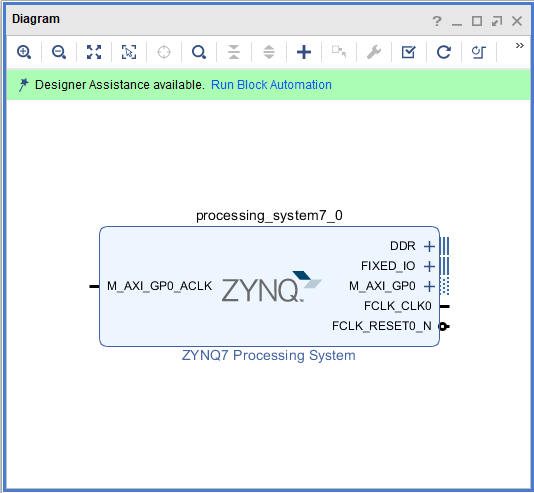

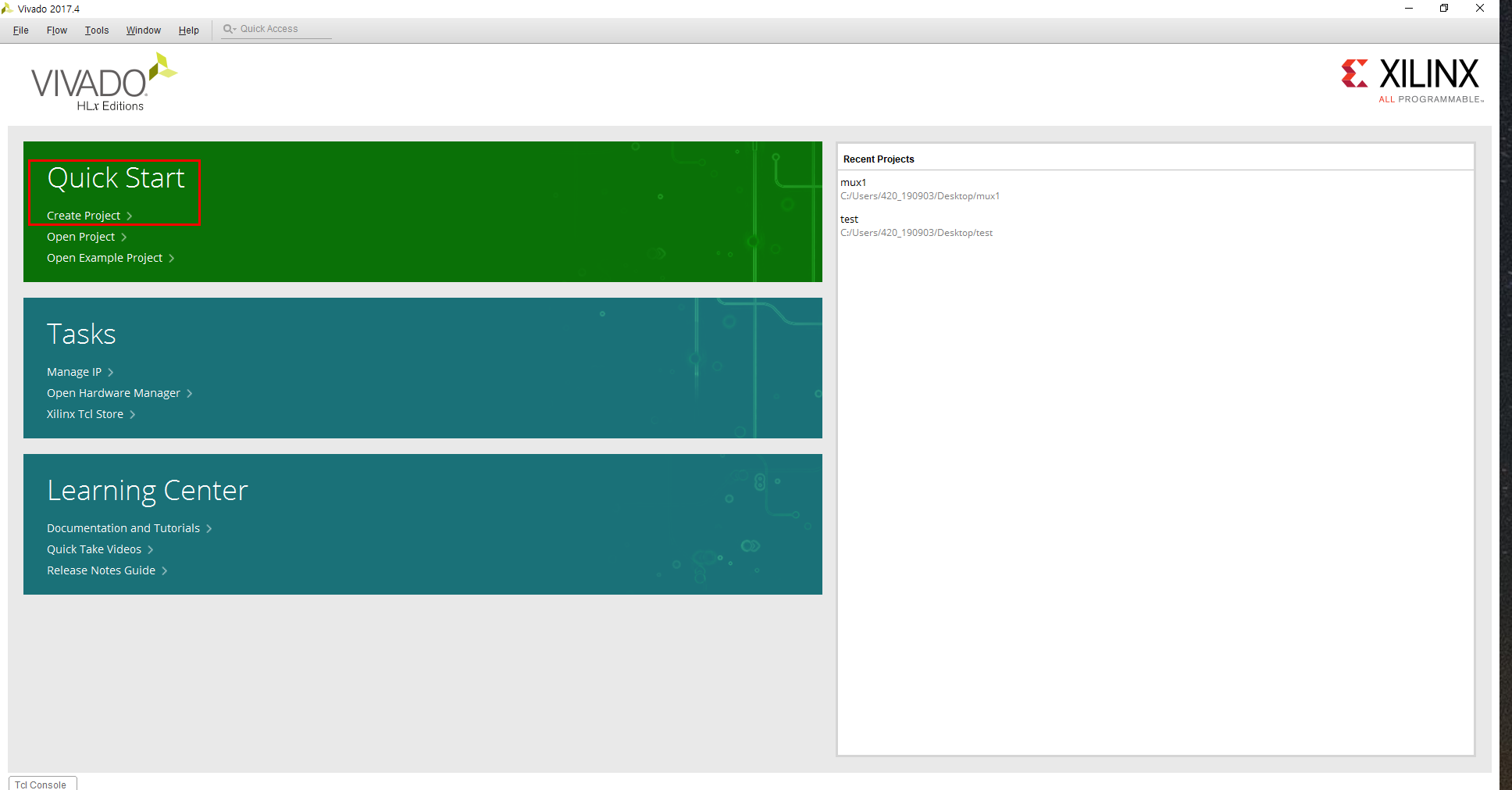

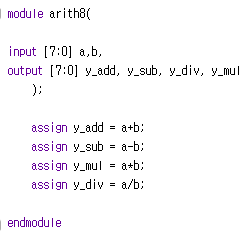

우선 사칙연산을 수행해주는 arith8이라는 이름의 모듈을 하나 만들어주자.

a와 b를 입력으로 받아 각각의 사칙연산 결과를 출력으로 내보내주는 모듈이다.

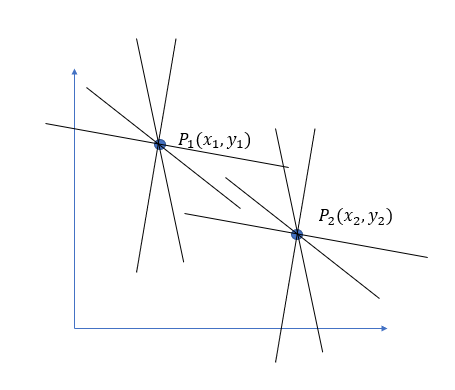

회로의 규모가 커지게 되면 하나의 모듈로 처리하기에는 적합하지 않은 경우를 만나게 되는데

이때 설계할 내용을 기능적인 측면과 회로의 양을 감안하여 하나의 모듈이 지나치게 커지지 않도록

적절한 크기로 분할하여 처리할 필요가 있다.

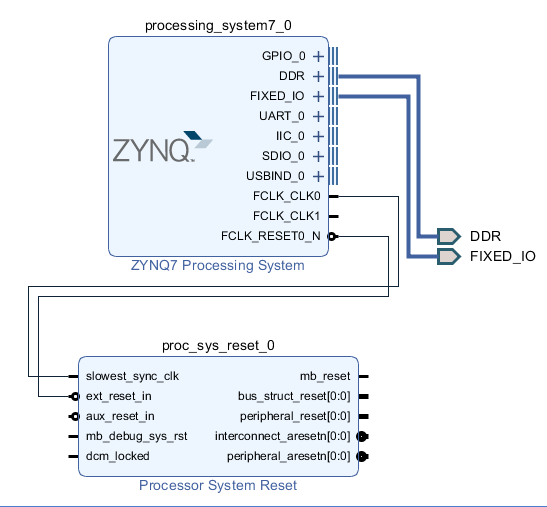

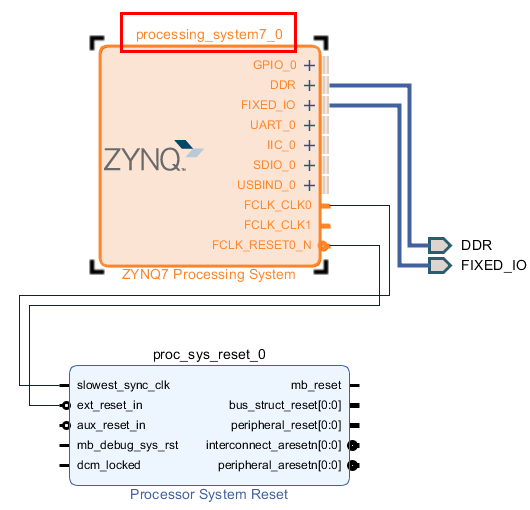

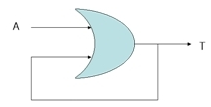

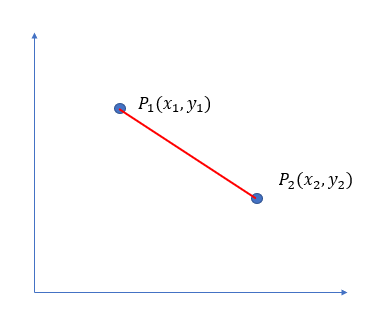

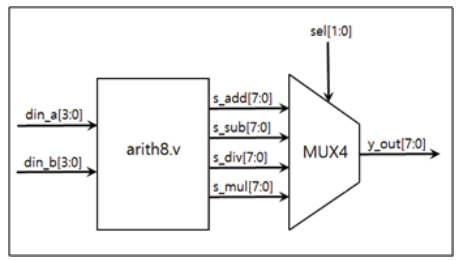

위의 그림은 a,b 입력을 받고 사칙연산을 수행하여 출력하는 과정을 도식화하여 나타낸 것이다.

앞에서 작성한 코드는 위의 그림에서 사각형으로 나타내어진 arith8.v에 해당한다.

그럼 위의 그림에서 나타내어진 것과 같이 din_a, din_b의 입력을 받아 최종적으로 y_out의 출력을 갖는

구조를 나타낼 때 이미 만들어진 arith8 모듈을 사용하여 위의 그림처럼 나타내어 보자.

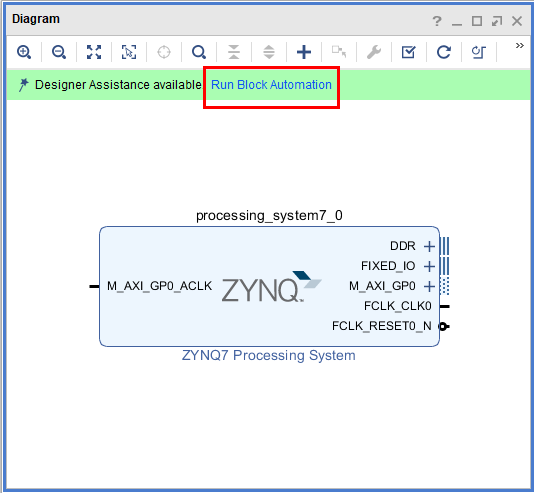

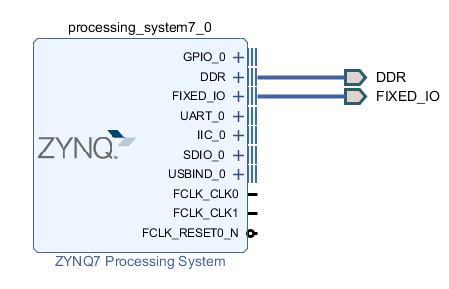

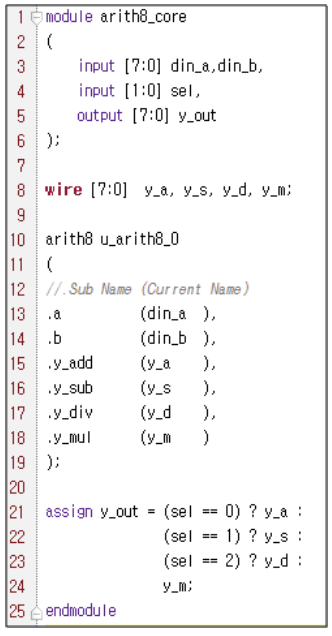

가장 먼저 큰 모듈인 arith8_core 모듈을 만들어주자.

이는 입력은 din_a, din_b, sel 을 갖고 출력으로 y_out을 갖고 있다.

그 다음 y_a, y_s, y_d, y_m 들을 선언해주는데 바로 아래에 arith8 모듈을 상위모듈로 하여

하위모듈인 u_arith8_0 모듈을 만드는 것을 볼 수 있다.

상위모듈인 arith8.v 에서 입력인 a와 b는 하위모듈에서 din_a, din_b로 맵핑해주고

상위모듈에서의 y_add는 하위모듈에서 y_a 로 맵핑, 그리고 이러한 방식으로 맵핑이 진행되게 된다.

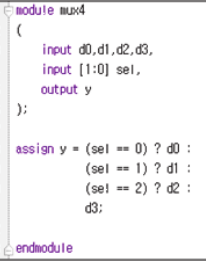

그리고 그 다음 맵핑된 y_a, y_s, y_d, y_m을 이용하여 MUX를 구성한 것을 볼 수 있다.

즉 arith8_core 모듈은 결론적으로 din_a, din_b, sel의 입력, y_out의 출력을 갖는 모듈인데

이를 표현하기 위해 arith8 모듈을 사용하였다.

arith8모듈은 입력이 a, b 이고 출력이 y_add, y_sub, y_mul, y_div인 모듈인데

이를 arith8_core에서 사용할 것이기에 맵핑을 통해 맞춰주는 과정이 필요하게 된다.

입력은 arith8_core의 입력과 arith8의 입력이 동일하게 사용되므로

.a (din_a),

.b (din_b), 와 같이 a와 b를 din_a, din_b 로 맵핑해주었고

arith8 모듈의 출력을 표현하고 다루기 위해서 y_a, y_s, y_d, y_m 신호를 만들어주어

사용하고 이를 통해 결과적으로 y_out의 출력을 나타내고 있다.

(참고로 하위모듈 이름이 u_arith8_0 인 이유는 arith8모듈의 under이라 u가 붙고 0번째, 1번째... 와 같이

순서대로 진행될 수 있기에 0을 붙여준다. 즉 arith8의 0번째 하위모듈이란 뜻을 담고 있다.)

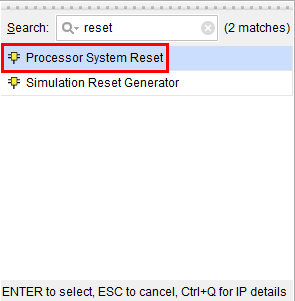

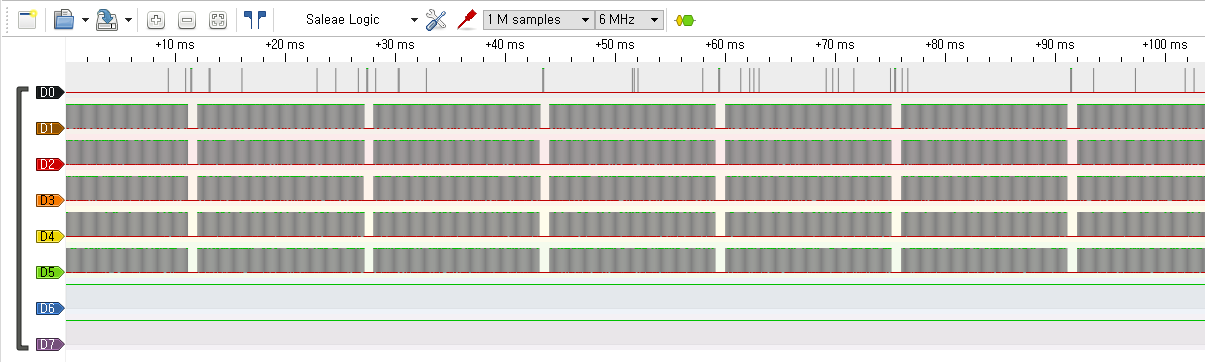

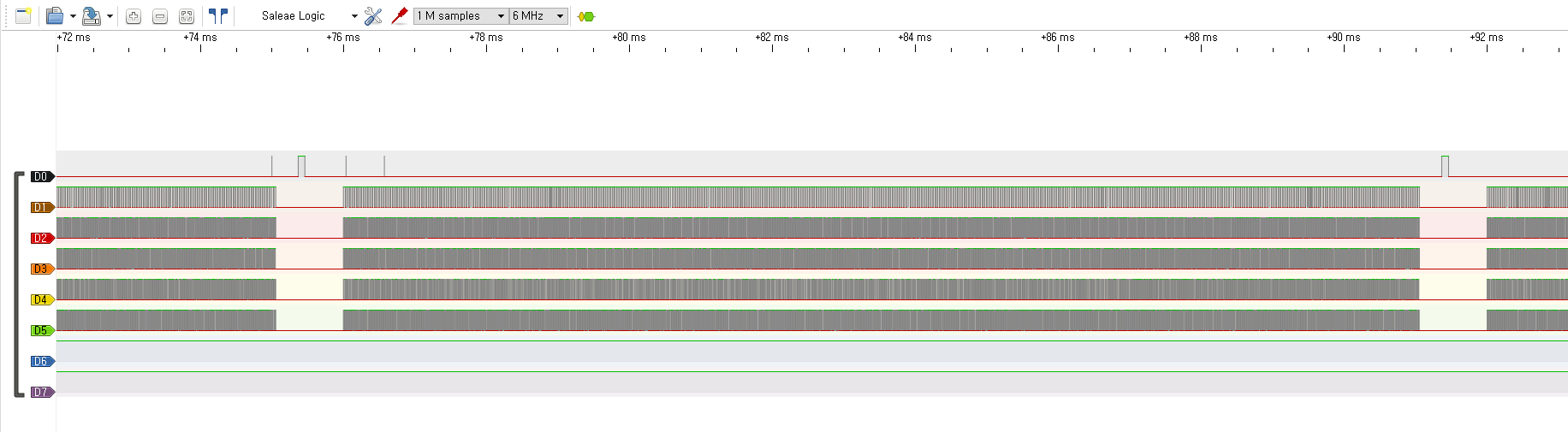

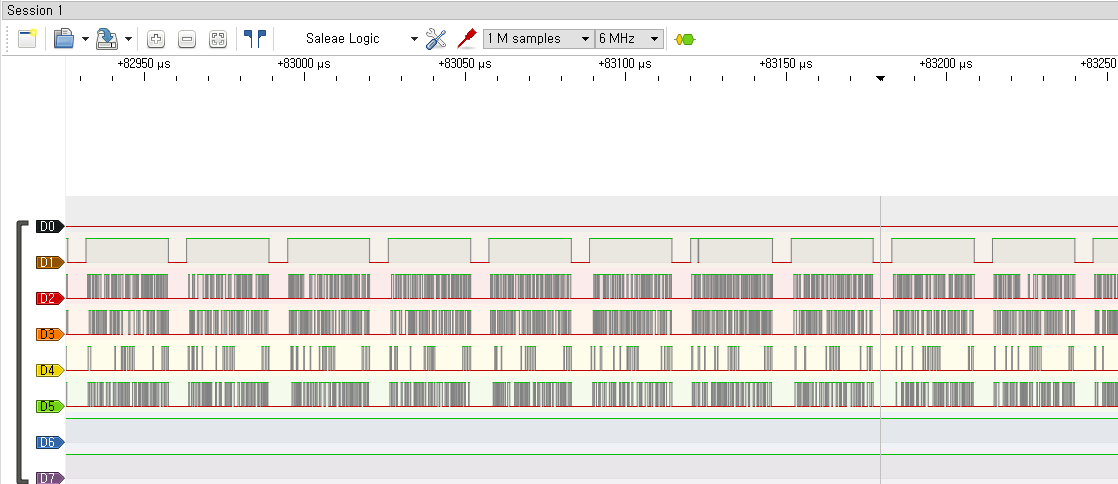

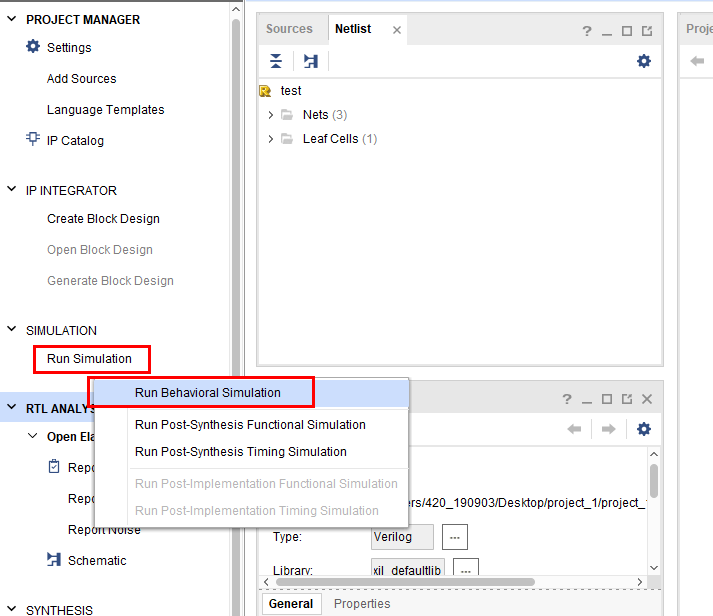

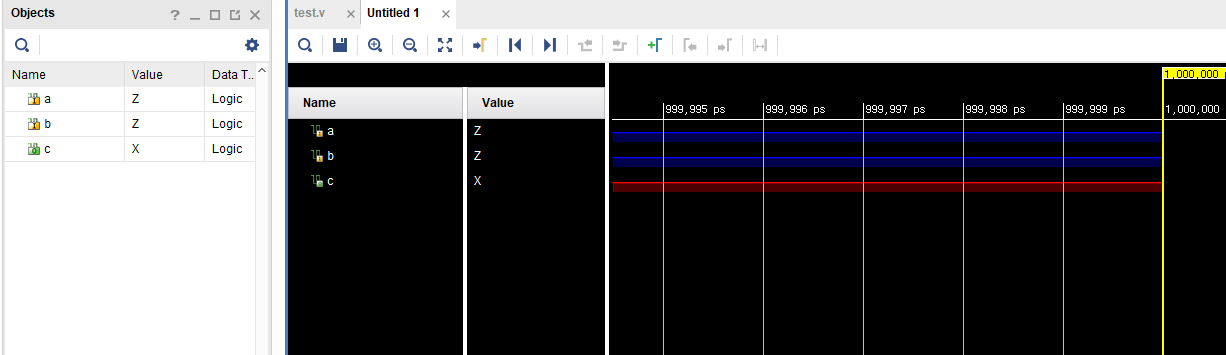

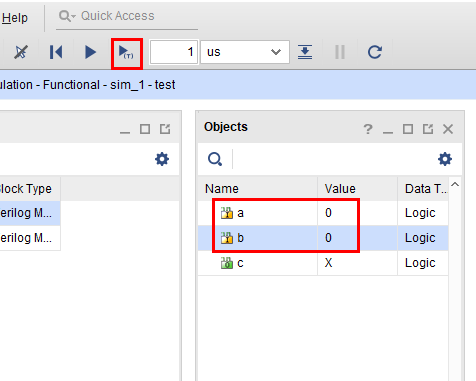

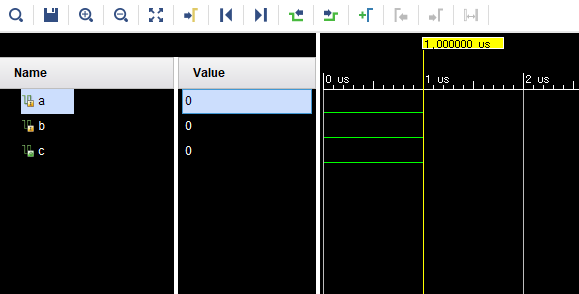

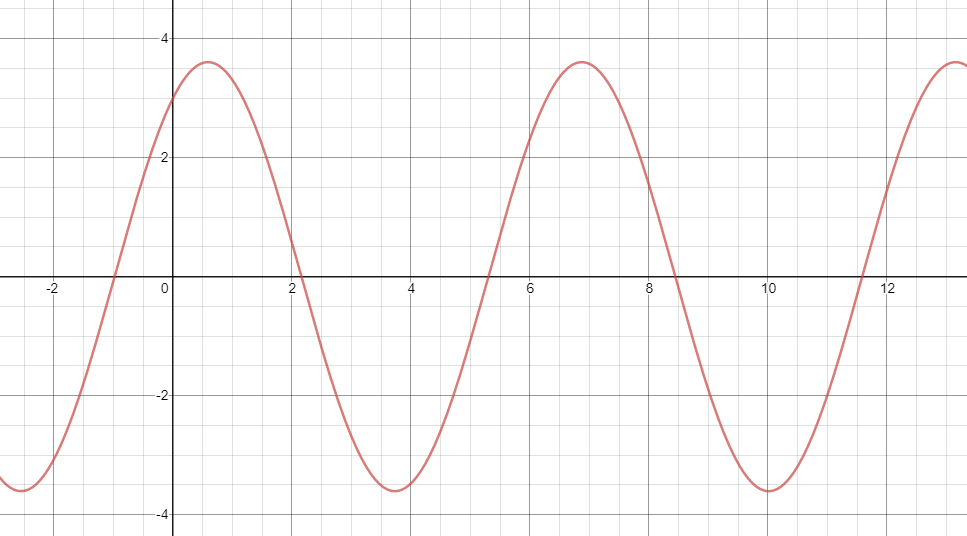

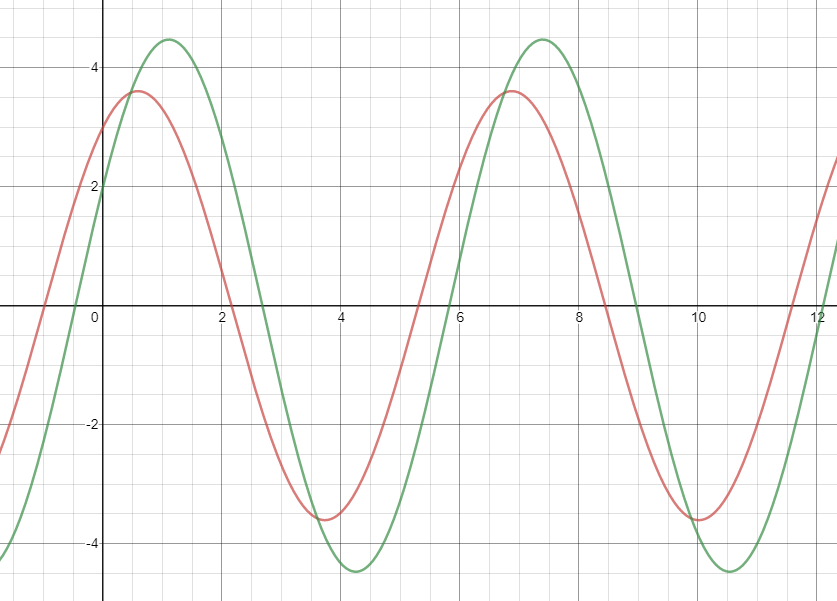

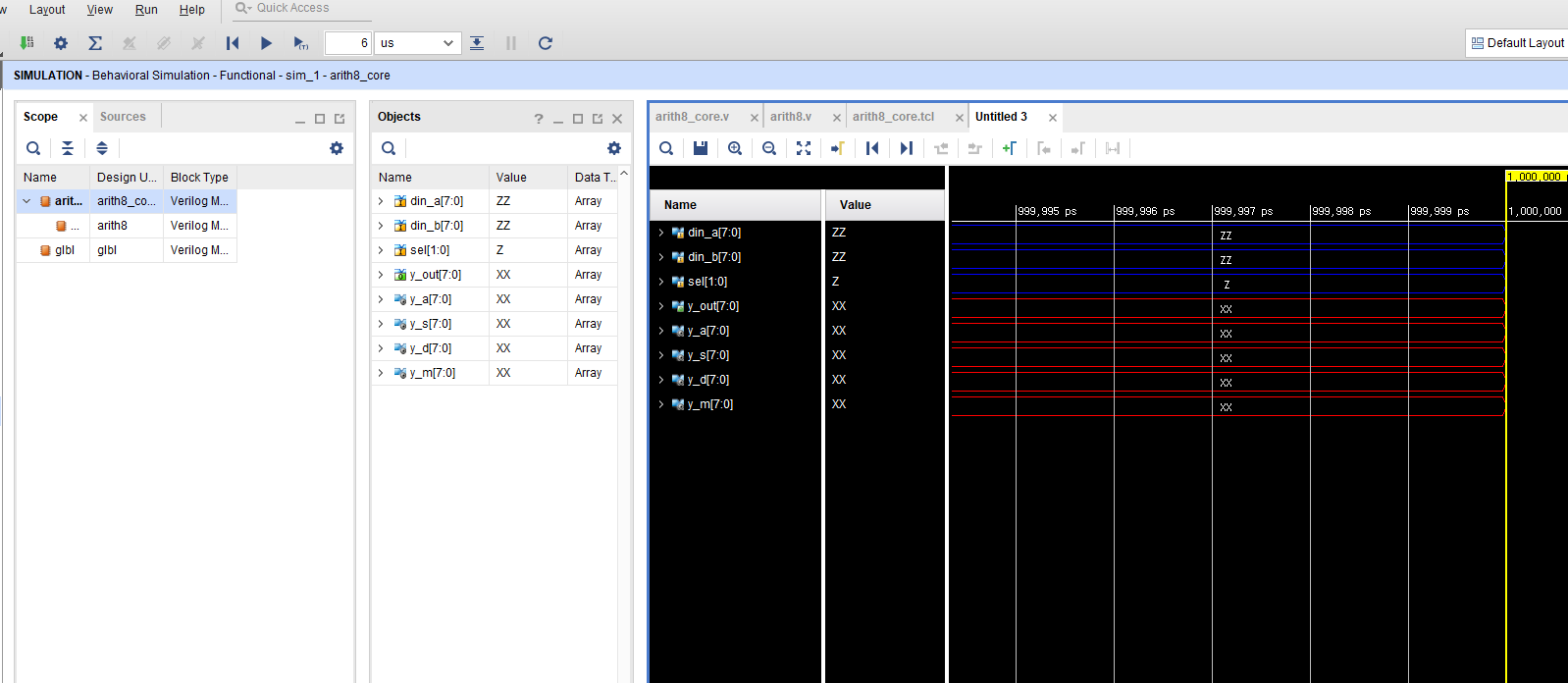

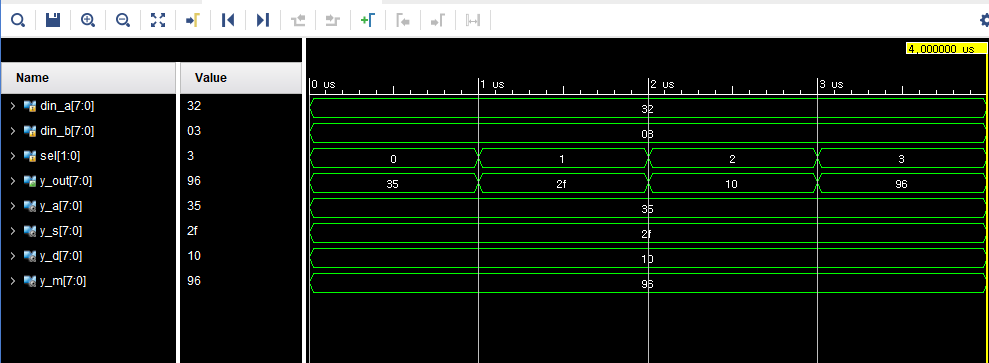

시뮬레이션을 실행하면 위와 같이 출력되는 것을 확인할 수 있다.

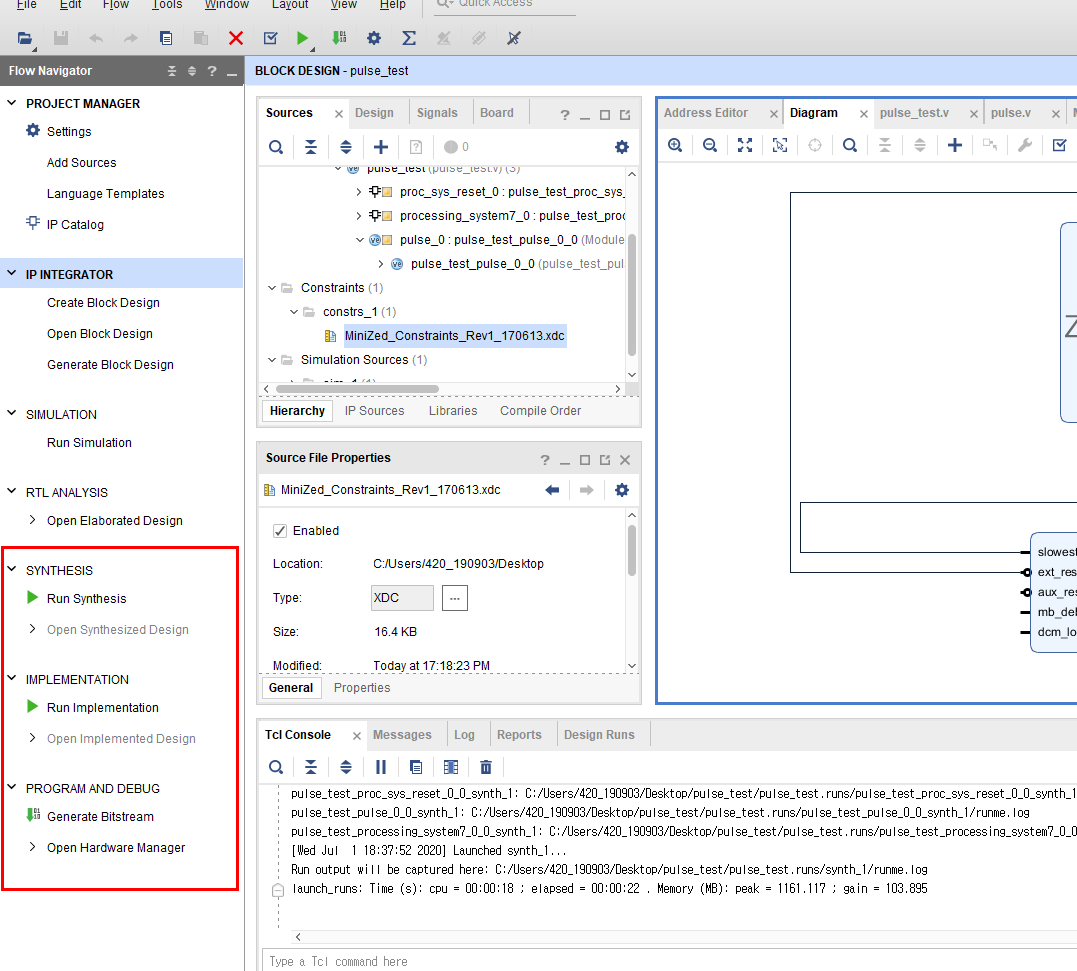

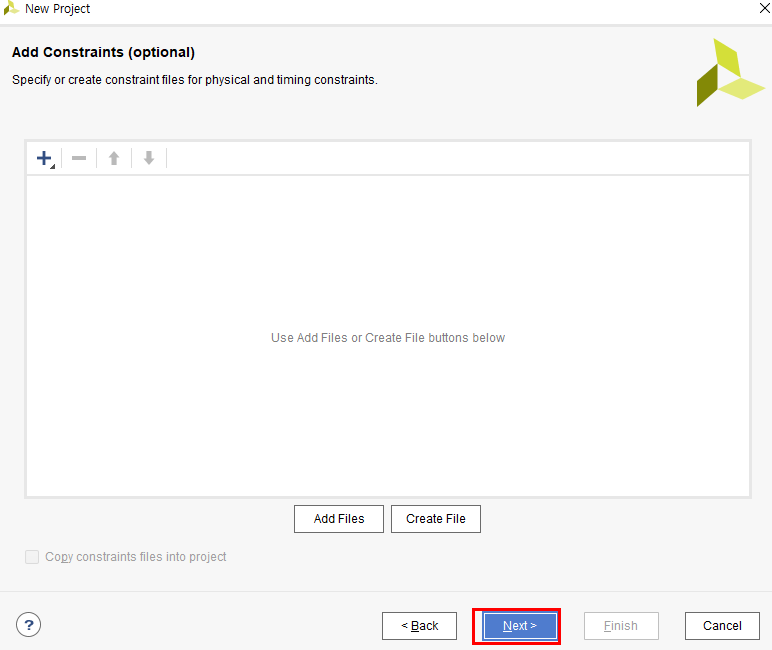

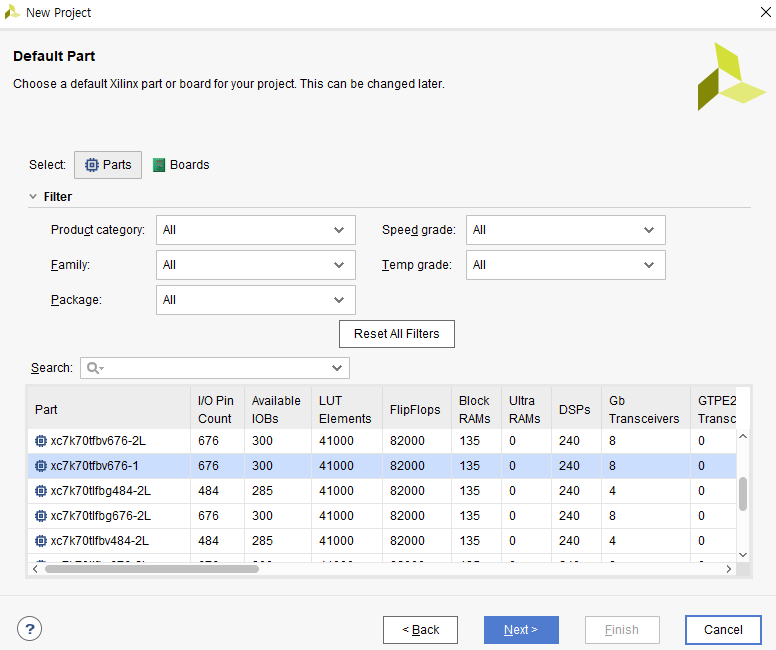

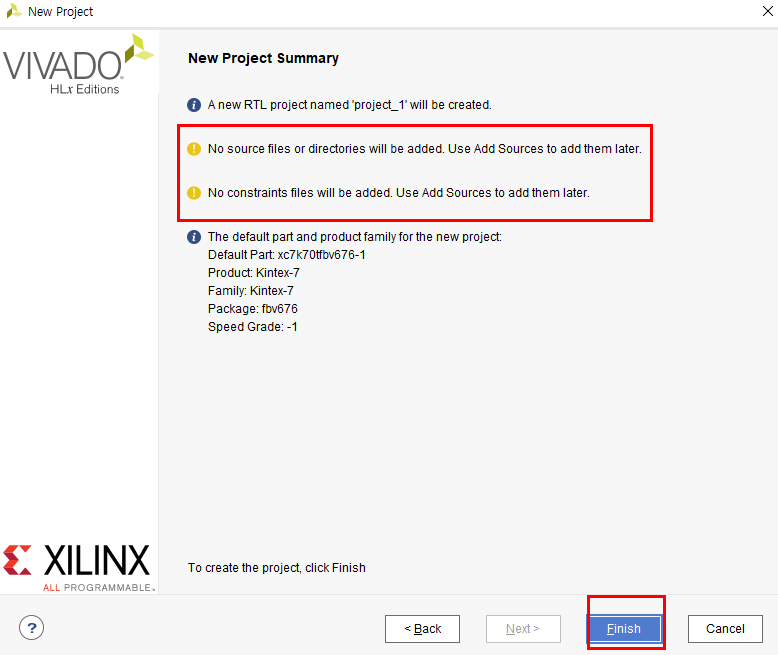

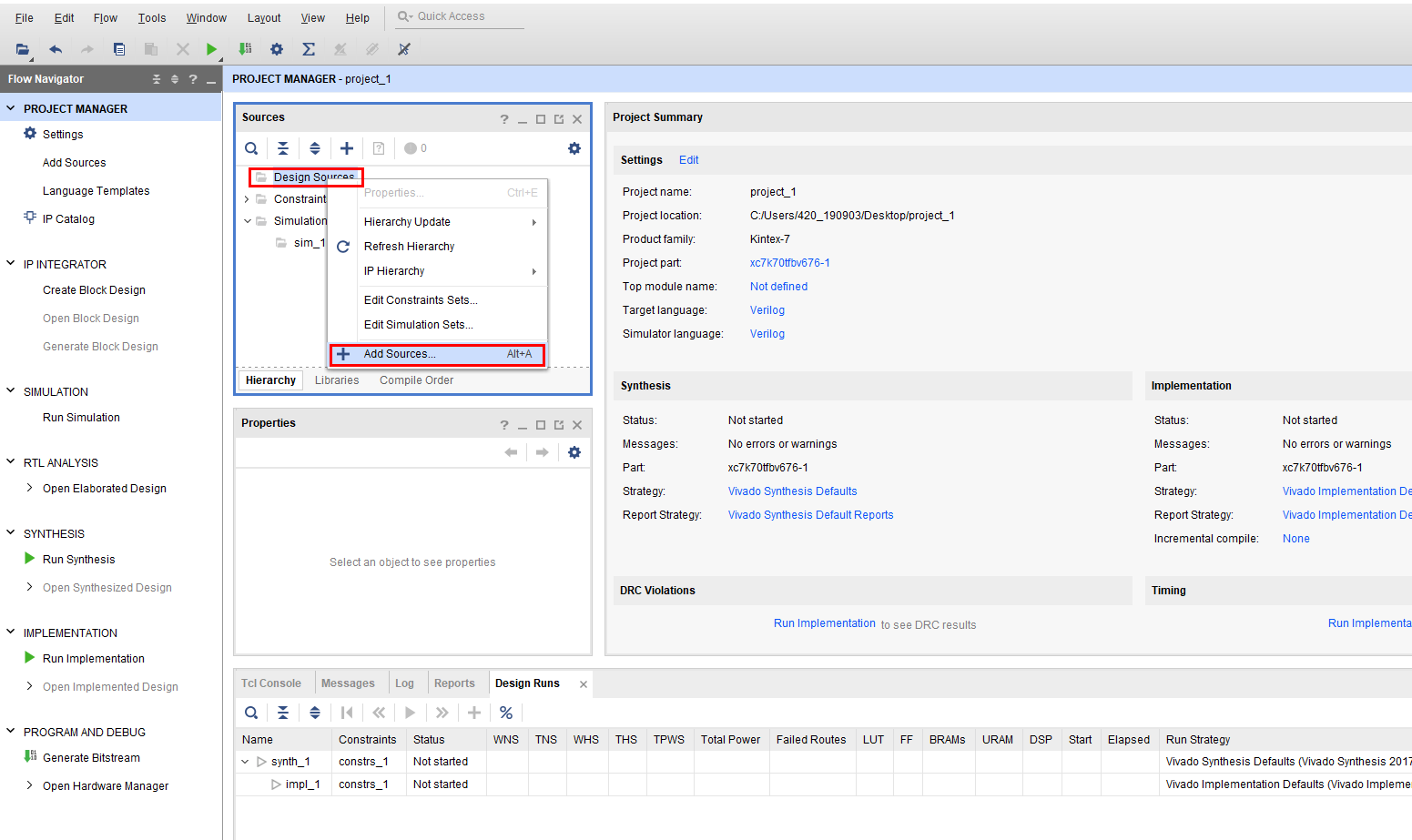

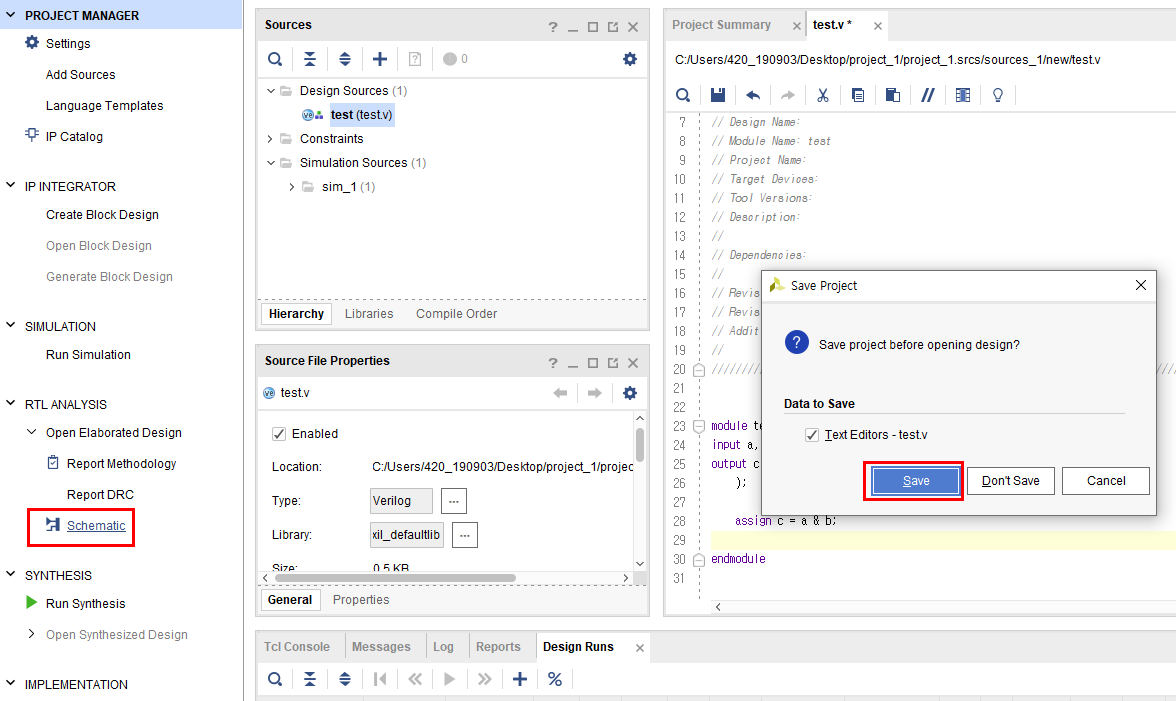

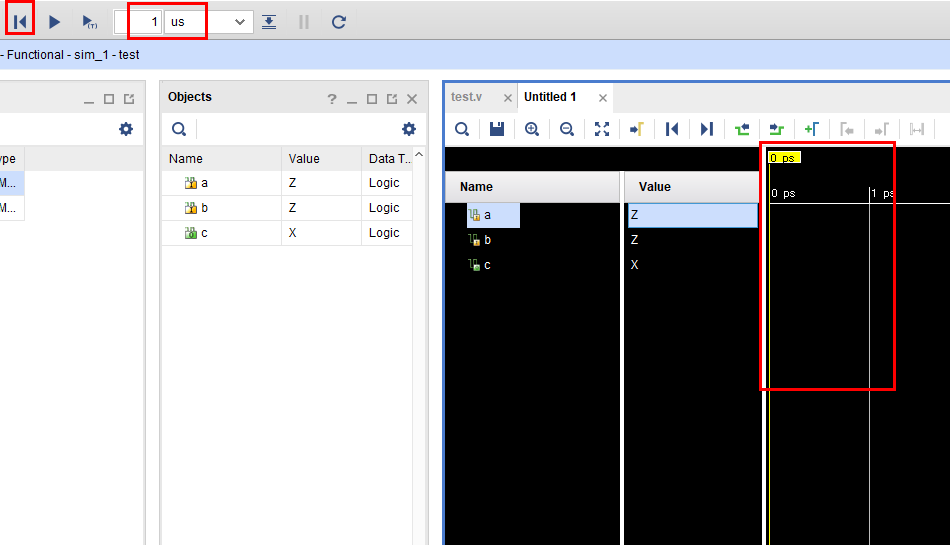

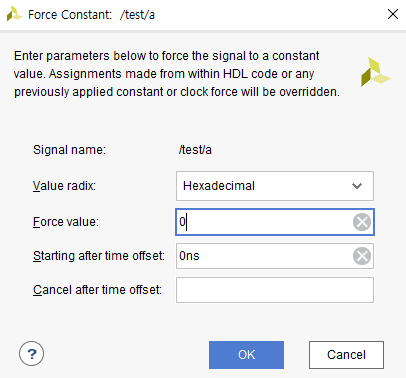

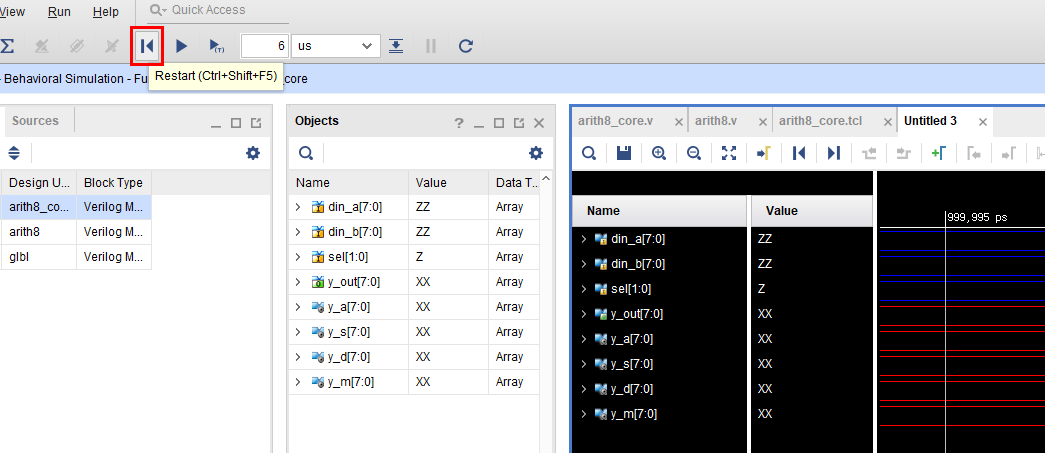

위의 Restart를 눌러준 후

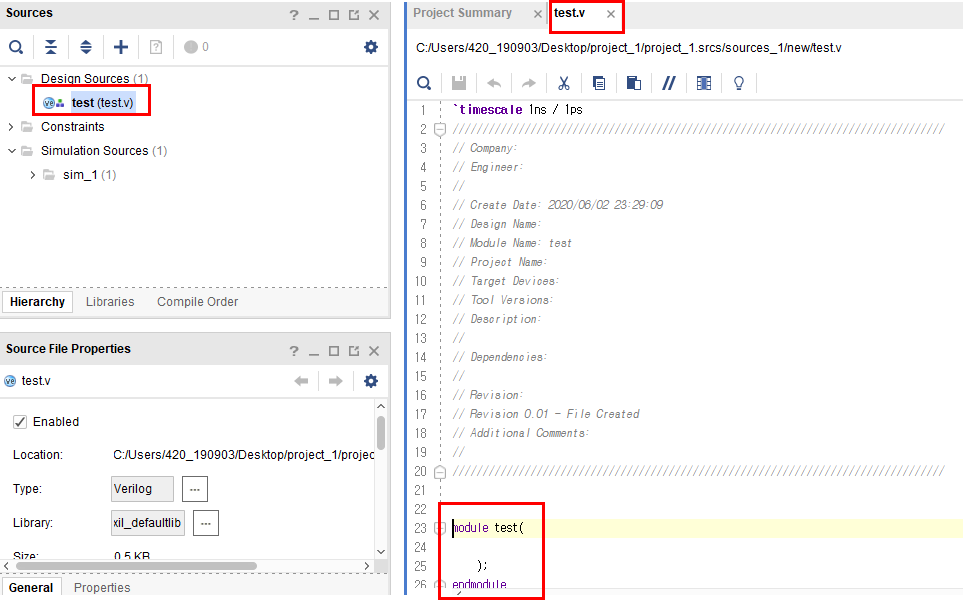

시뮬레이션 파일을 저장해준다.

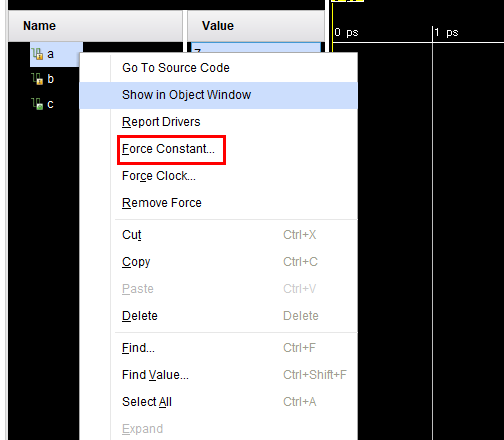

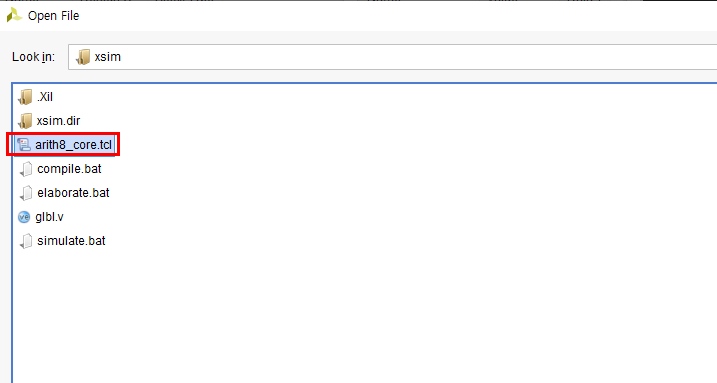

그리고 openfile을 이용하여 tcl파일을 열어주고

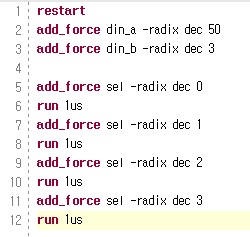

아래와 같이 코드를 작성한 후 저장하여 준다.

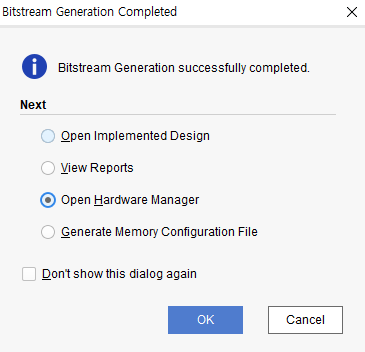

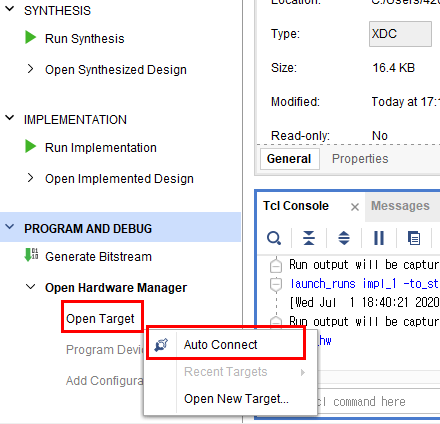

작성이 완료되었으면

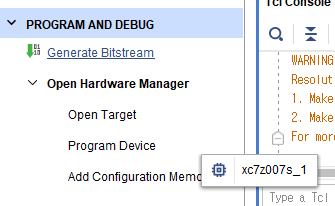

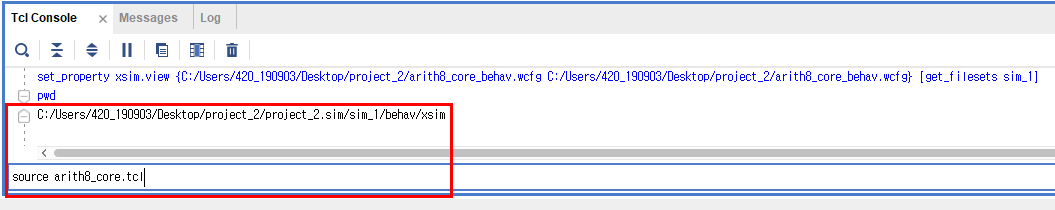

이렇게 tcl파일이 있는 경로로 이동한 후

source 모듈명.tcl 입력

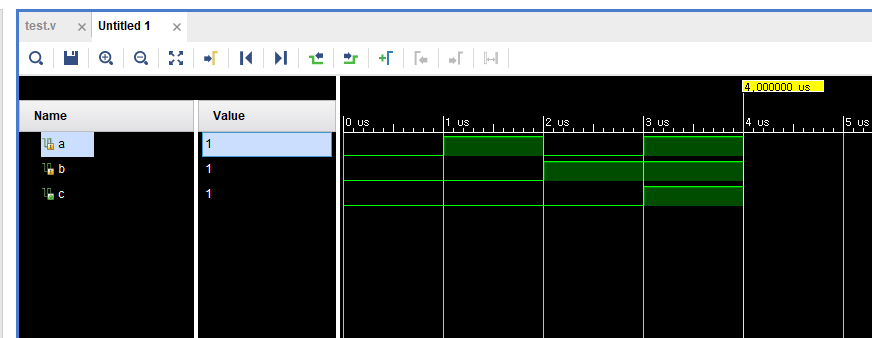

그럼 위와 같이 아름다운 시뮬레이션 결과가 출력된다.

'FPGA > Verilog 공부' 카테고리의 다른 글

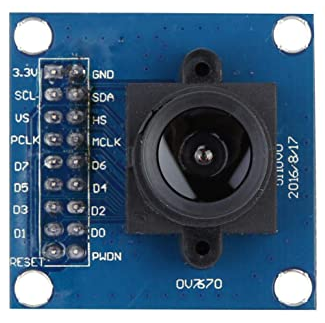

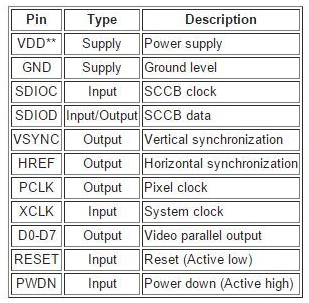

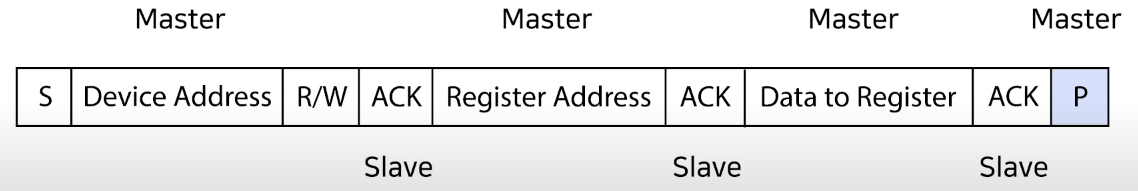

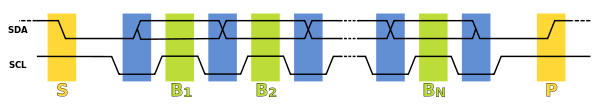

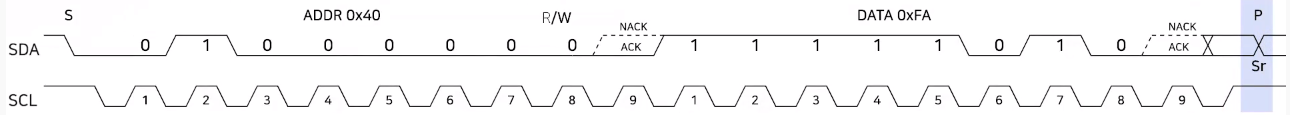

| Verilog 코드를 이용하여 OV7670 카메라모듈 사용하기(SCCB 통신) (1) | 2020.12.29 |

|---|---|

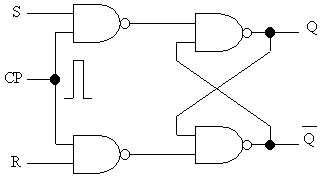

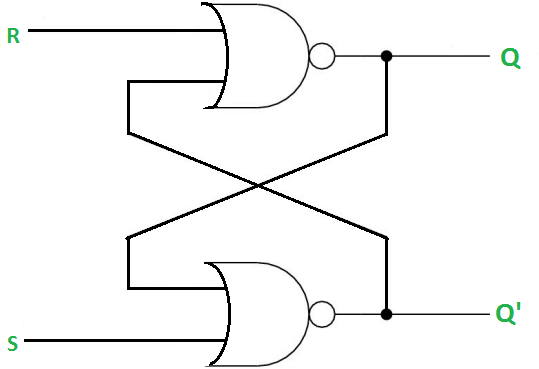

| F/F(플립플롭), Latch(래치), 순차회로, 조합회로 (0) | 2020.12.29 |

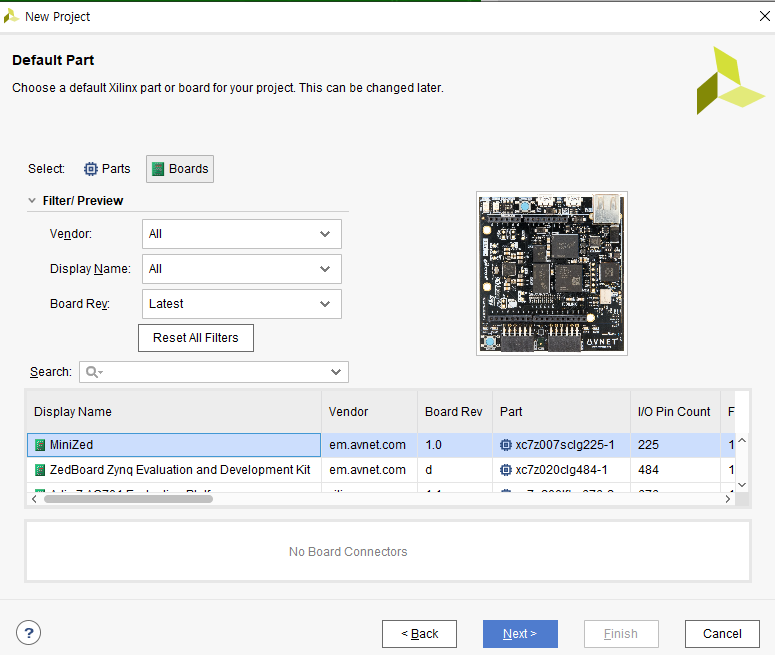

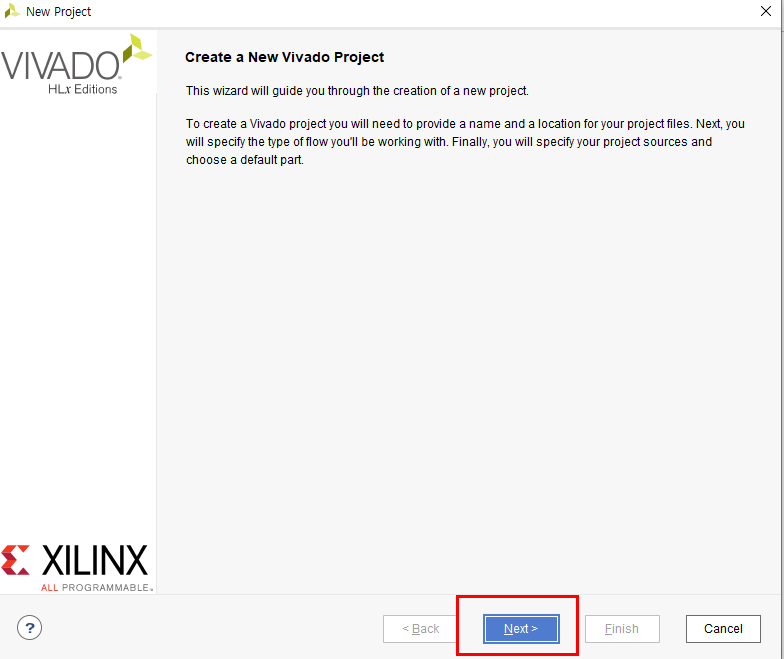

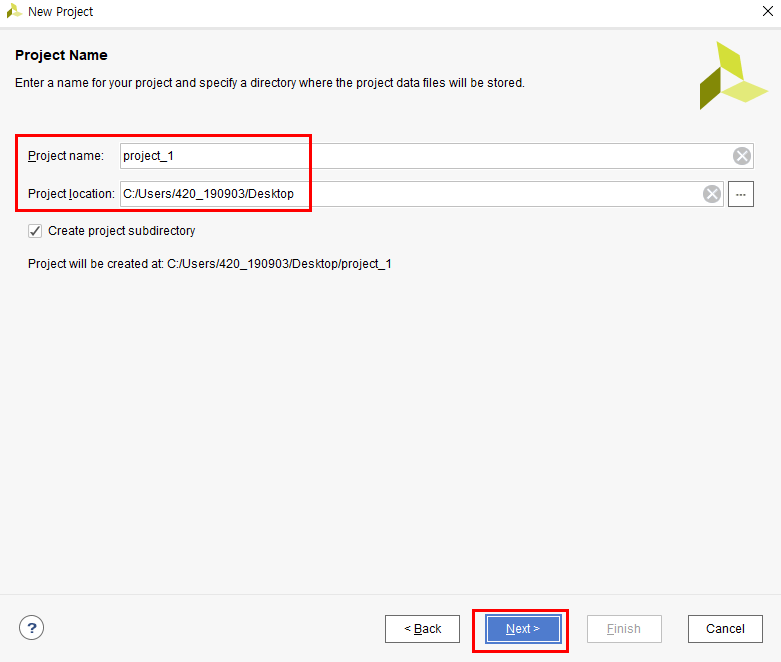

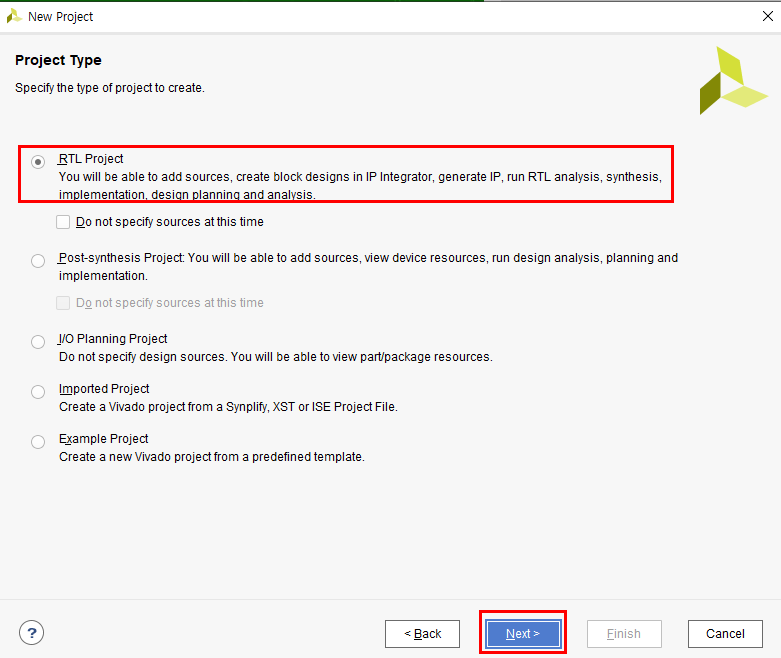

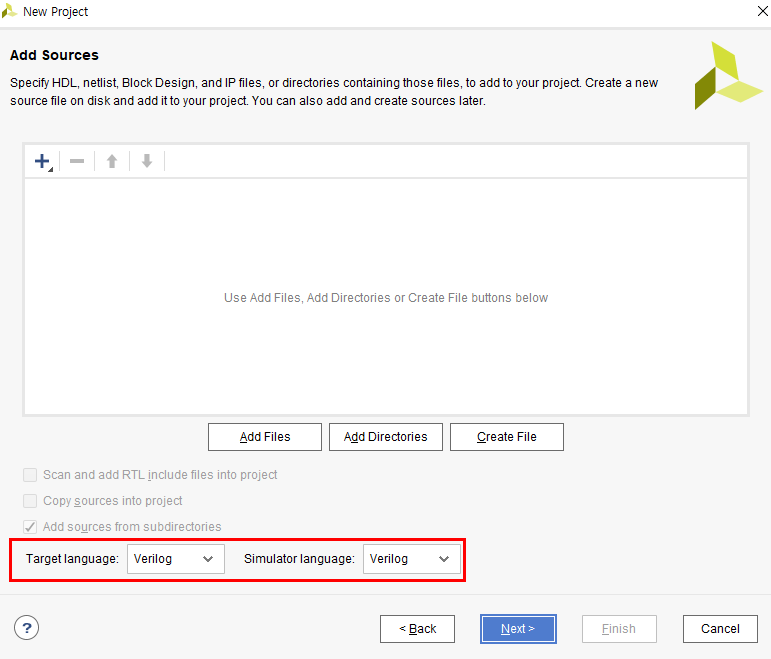

| VIVADO 사용법(완전 기초) (2) | 2020.12.29 |

| Verilog를 통한 MUX회로 구현 (0) | 2020.12.29 |

| Verilog를 사용하여 Disparity Map 생성_(1) (0) | 2020.08.28 |