베릴로그를 공부하다보면 플립플롭과 래치, 순차회로, 조합회로에 관한 얘기가 많이 나오게 된다.

* 순차회로, 조합회로

간단하게 이전 입력을 기럭하는 부분이 있는 회로라면 순차회로, 이전 입력을 기억하지 않는다면 조합회로로

볼 수 있다.

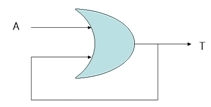

위의 경우 A,B,C,D의 입력값들에 의해 출력 T가 결정되게 된다. 이는 조합회로로 볼 수 있다.

다음은 순차회로이다.

위의 회로는 A값에 1이 한번 입력되게 되면 T값은 계속 1을 출력하게 된다.

A에 1이 들어가게 되면 OR게이트이므로 무조건 1을 출력하게 되고 T는 1, 그리고 이 값이 다시 OR게이트에

입력으로 들어가게 된다. 이 때 A값이 0으로 바뀌었다고 해도 이전의 값이 1이었기에 T는 계속해서 1이 출력되게

된다.

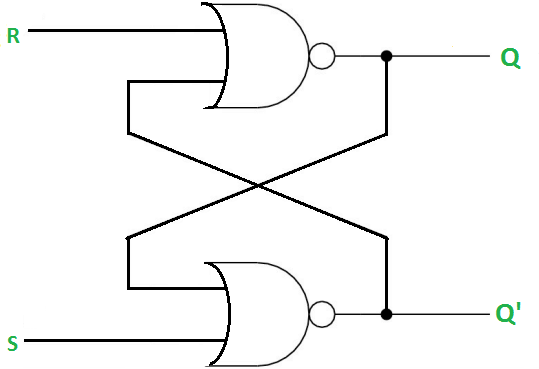

1비트의 정보를 저장하는 회로를 플립플롭(flip-flop)이라 한다.

위의 그림은 SR플립플롭을 도식화 한 것이다.

우선 S값에 0, R값에 1이 입력되었다고 가정해보자.

R값은 1이기에 NAND게이트를 통해 0이 출력되게 되고

이는 다시 NAND를 통해 1이 출력되어 Q'은 1이 출력되게 된다.

그리고 S는 0이기에 NAND를 통해 1이 출력되고 이는 다시 NAND를 통해

위에서의 Q'값 1을 통해 Q는 0이 출력되게 된다.

그리고 S와 R 신호 모두 0이 되면 이전의 상태를 유지하게 된다.

그럼 S값에 1, R값에 0이 입력된다고 보면

S의 NAND는 0이 출력되고 되고 다시 NAND의 입력으로 들어가게 되어 Q로 1이 출력되게 된다.

그리고 R은 0이기에 NAND를 통해 1이 출력되게 되고 이는 다시 Q신호 1과 함께 NAND로 들어가

Q'은 0이 출력되게 된다.

그리고 이 또한 S와 R 신호 모두 0이 되면 이전의 상태를 유지하게 된다.

참고로 S나 R 신호 중 하나가 1로 되지 않은 상태에서 S와 R 신호 모두 0이 되게되면 에러가 발생하게 되고

두 신호 모두 1이 되게 되면 출력은 Q와 Q' 모두 0이 되게 된다.

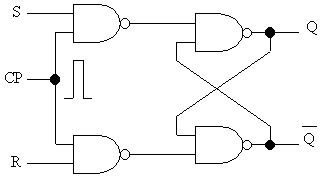

위는 SR Latch의 이미지인데 보면 플립플롭과 다르게 CP신호가 없음을 확인할 수 있다.

즉 Latch와 F/F의 차이는 클럭입력을 가하게 되면 F/F

클럭입력을 가하지 않으면 Latch로 볼 수 있다.

이를 순차회로라고 하고 플립플롭과 래치는 이러한 방식으로 값을 저장하게 되는 것이다.

'FPGA > Verilog 공부' 카테고리의 다른 글

| 계층구조 설계를 위한 Verilog HDL (0) | 2020.12.29 |

|---|---|

| Verilog 코드를 이용하여 OV7670 카메라모듈 사용하기(SCCB 통신) (1) | 2020.12.29 |

| VIVADO 사용법(완전 기초) (3) | 2020.12.29 |

| Verilog를 통한 MUX회로 구현 (0) | 2020.12.29 |

| Verilog를 사용하여 Disparity Map 생성_(1) (0) | 2020.08.28 |