MiniZed 보드에 보면 Pmod 포트가 있다.

여기에 Pmod VGA 어뎁터를 연결하여 모니터에 출력을 하고자 한다.

https://timetoexplore.net/blog/arty-fpga-vga-verilog-01

FPGA VGA Graphics in Verilog Part 1 — Time to Explore

This tutorial series introduces video graphics programming using FPGAs, starting with creating a VGA driver and moving onto more advanced features including bitmaps, sprites and effects. FPGAs excel at high-speed I/O and custom logic: you'll be surprised h

timetoexplore.net

위의 블로그를 참고하여 실행하였다.

디지털 신호들이 어떻게 VGA케이블을 통해 모니터에 출력될 수 있는지는 본 게시물에서 다루지 않도록 하겠다.

이를 자세히 설명해주는 많은 한글 자료들이 많이 있기에 참고하면 될 것 같다.

본 게시물에서는 그냥 코드를 가져와 어떻게 실행하는지 기본적인 내용만 다룬다.

우선 프로젝트를 하나 생성하여 준다.

이때 minized의 Constraint 파일도 등록하여 진행하고 보드도 minized를 선택하여 프로젝트를 생성해준다.

위와 같이 프로젝트가 생성된 것을 확인할 수 있다.

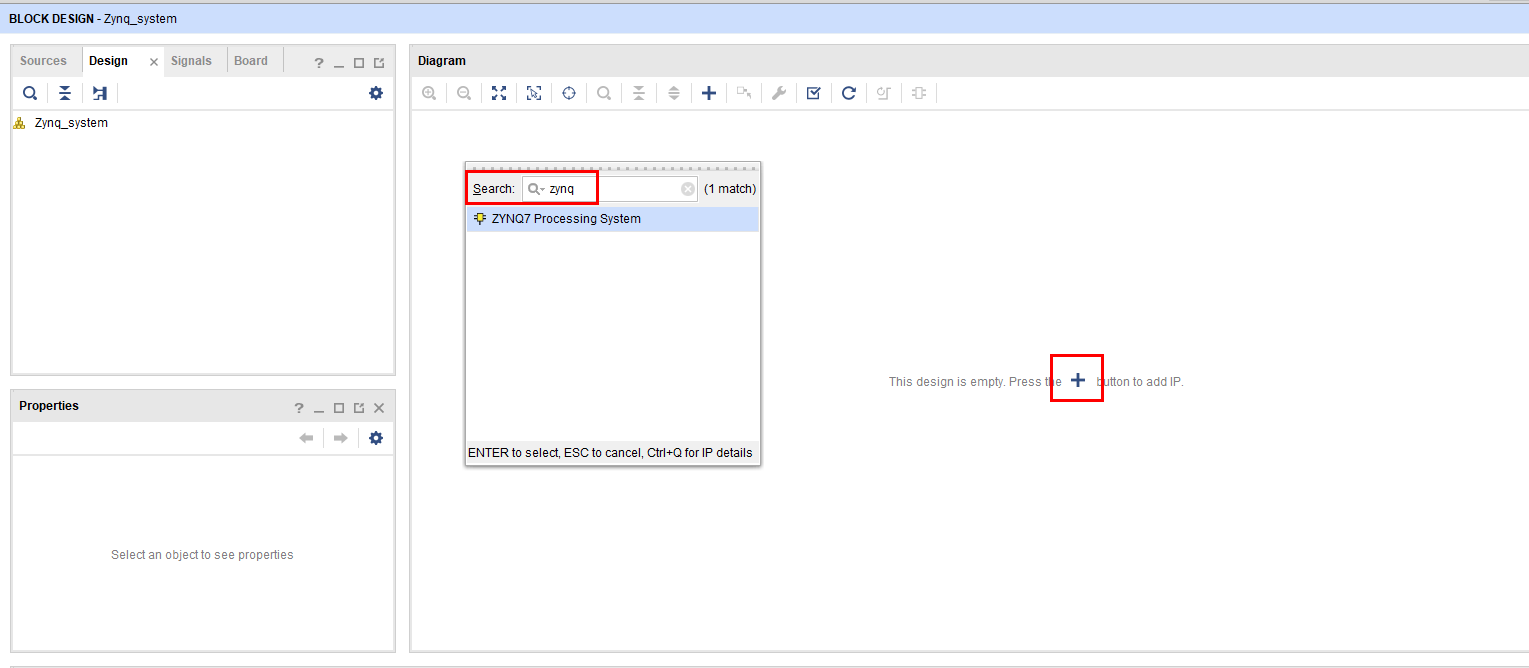

프로젝트 생성 후 좌측에 보이는 'IP INTEGRATOR' 에서 Create Block Diagram을 선택하면 위의 사진과 같이 윈도우가 하나 뜨게 되는데 여기서 Design name을 적어준 후 OK를 누른다.

위와 같이 Diagram 창의 가운데 보이는 '+'를 클릭하면 검색창이 뜨게 되는데 zynq를 입력하면

'Zynq7 Process System'이 보이게 된다.

이를 더블클릭하여 생성하여 준다.

위와 같이 IP가 생성되게 되고 이름을 더블클릭하면 아래와 같은 창이 뜨게된다.

위의 창이 뜨면 'Clock Configuration' 항목에서 'PL Fabric Clocks', 그리고 아래 목록들 중 가장 위의 CLK0 항목만

체크한 후 OK를 누른다.

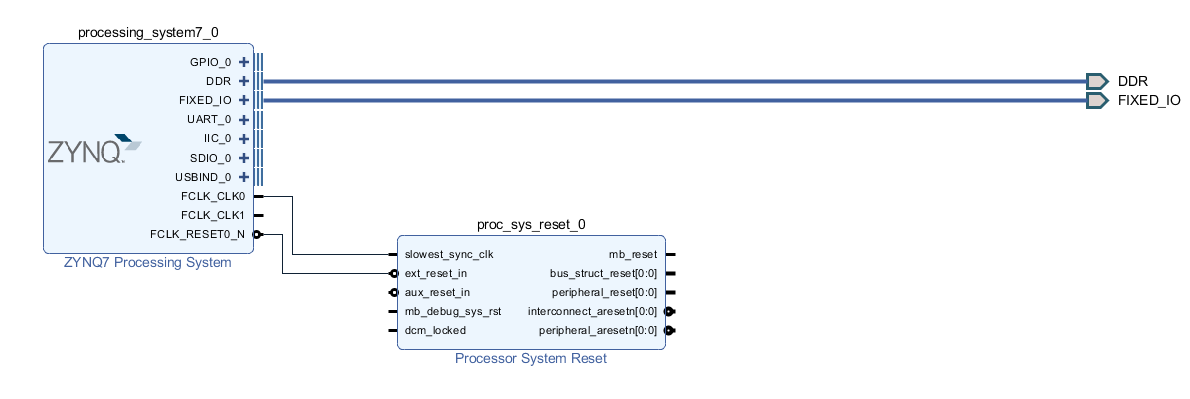

그리고 위의 'Zynq7 Process System' IP를 생성하였을때와 같이 'Processor System Reset' IP도 추가하여 준다.

그 후 아래와 같이 선을 이어준다.

그리고 상단의 'Run Block Automation'을 클릭하여준다.

아래는 그 결과화면이다.

그럼 이제 소스를 입력해주자.

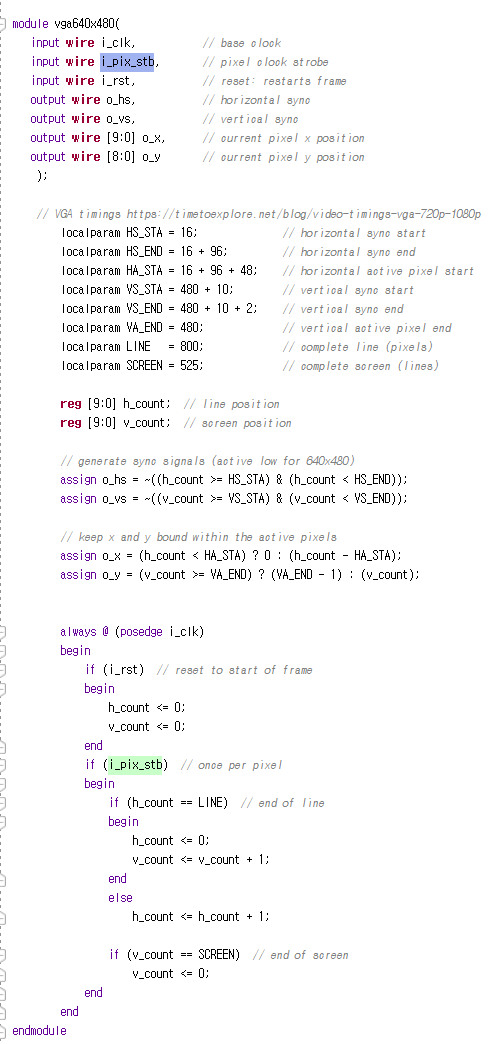

vga640x480 이라는 이름의 모듈을 만들어주자.

그 다음 top모듈을 생성하여 준다.

위의 문장 중

always@(posedge CLK)

{pix_stb, cnt} <= cnt + 16'h4000;

이라는 문장이 있다.

이 부분은 100MHz의 CLK 펄스를 25MHz로 나눠주기 위한 과정으로 {a, b} 는 Verilog의 결합연산자 이다.

결합연산자란 중괄호 { }에 의해 묶인 두 개 이상의 표현이 갖는 비트들의 결합으로

위와 같은 특징이 있다.

즉 중괄호 안의 값들에 대한 비트를 순서대로 그냥 붙인다는 특징이 있다.

따라서 위의 과정에서는

{pix_stb, cnt} 로 사용되었는데 pix_stb는 1비트의 크기를 갖는 값이고

cnt는 [15:0] 의 16비트 크기이므로 {pix_stb, cnt}는 총 17비트 크기의 값을 갖게 된다.

또한 cnt는 16비트의 값으로 초기에는 0의 값을 갖게 되고

16'h4000 은 2진수로 나타내면 16'b 0100 0000 0000 0000 의 값을 갖게 된다.

always@(posedge CLK) 에 의해 매 CLK 펄스에 맞추어

처음에는

0000 0000 0000 0000

+0100 0000 0000 0000

= pix_stb, 0000 0000 0000 0000

이 되고 두번째 posedgeCLK에서는

0000 0000 0000 0000

+0100 0000 0000 0000

= pix_stb, 0100 0000 0000 0000

0100 0000 0000 0000

+0100 0000 0000 0000

= pix_stb, 1000 0000 0000 0000

1000 0000 0000 0000

+0100 0000 0000 0000

= pix_stb, 1100 0000 0000 0000

0000 0000 0000 0000

+0100 0000 0000 0000

= pix_stb, 0000 0000 0000 0000 이 되고 pix_stb의 값이 1이 되게 된다.

그리고 위의 과정을 다시 반복하여 pix_stb 값은 다시 0이 되게 되고 따라서 결과적으로

CLK의 펄스 주기를 1/4 로 나누는 효과가 발생하게 된다.

즉 100MHz의 CLK를 통해 25MHz의 pix_stb 신호를 만들 수 있게 된다.

그렇게 되면 Design Source에 아래와 같이 뜨게 된다.

top 모듈에서 vga640x480 모듈의 신호를 사용하기에 위와 같이 뜨게된다.

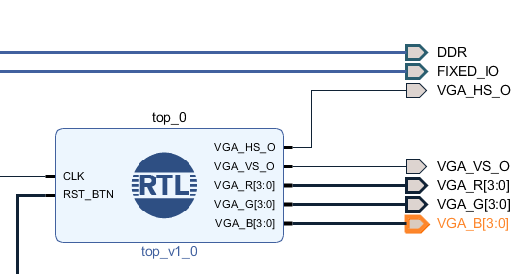

그럼 이제 다시 Diagram으로 돌아와서 모듈을 추가해준다.

그럼 생성한 모듈이 2개이므로 아래와 같이 2개 항목이 뜨게 된다.

하지만 top모듈 안에서 vga640x480 모듈을 가져와 사용하므로 Diagram에서는 top모듈만 추가하여준다.

그리고 위와 같이 선을 연결하여준다.

그리고 top 모듈 각각의 출력포트를 우클릭하면 다음과 같이 뜨게된다.

Create Port를 선택하여 진행하고 이를 모든 출력에 대해 진행하여준다.

그 다음 좌측의 Sources 목록에서 Zynq_system 항목을 우클릭 한 후 Create HDL Wrapper 선택

그럼 아래와 같이 top모듈과 그 하위 vga640x480 모듈이 추가되었음을 확인할 수 있다.

그 다음 Zynq_system_wrapper을 우클릭한 후 Set as Top 을 선택

그 후 .xdc 파일을 열어 minized의 포트와 모듈의 출력신호를 mapping하여준다.

Minized의 포트관련 정보는 첨부파일에 있다.

여기까지 완료되었으면 Synthesis와 Implementation, generate Bitstream을 차례차례 실행하여준다.

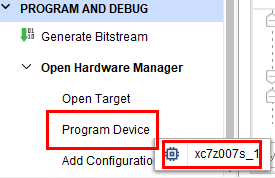

Generate Bitstream까지 완료되었으면 아래 사진과 같이 OpenTarget, Auto Connect를 실행

연결 되었다면 Program Device에서 해당 장치를 선택하여준다.

그리고 Bitstream파일을 장치에 프로그래밍해준다.

화면에 출력되는 것을 확인할 수 있다.

'FPGA' 카테고리의 다른 글

| MiniZed 를 통한 Pulse 출력 (0) | 2020.12.29 |

|---|---|

| Tera Term(테라텀)을 사용하여 FPGA 보드 다루기 (0) | 2020.09.23 |

| Minized를 다루기 위한 Vivado 프로젝트 설정 (0) | 2020.06.30 |