Vivado tool을 사용하여 작업하다보면 Simulation을 사용하는 경우가 많은데

아주 간단한 사용법을 적어두려고 한다.

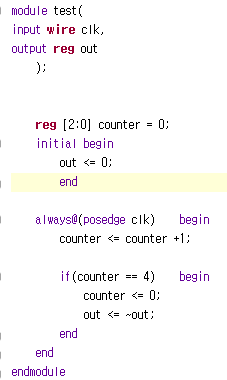

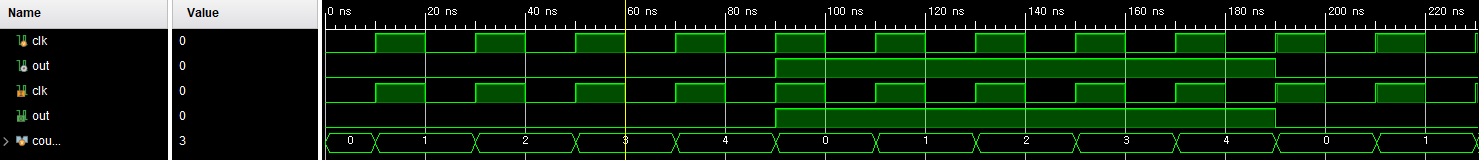

위와 같은 아주 간단한 모듈을 만든다.

입력은 클럭을 갖고 하나의 출력포트를 갖는 형태이다.

3Bit 크기의 counter을 만들어주고

counter값이 4가 되게 되면 out의 신호가 반전되는 모듈이다.

가장 먼저 위의 clk는 wire로 만들어주었는데

입력포트이기에 이 부분은 clk신호를 생성해주는 곳과 선으로 연결되게 될 것이다.

따라서 이 부분은 wire로 생성해 주었다.

그 다음은 out 출력포트인데 이 부분은 출력되는 값을 저장하여 갖고있어야 하기에 reg 형태로 만들어주었다.

따라서 출력포트는 0 혹은 1의 값을 갖게 되고 그 다음으로 4까지의 값을 갖도록 해주기 위해

3Bit 크기의 counter 을 만들어준다.

모든 Reg에 대해서는 초기화가 필요하다.

counter의 경우 모듈 중간에 생성된 부분이기에 중간에 초기화를 해주면 되고

out의 경우 모듈의 포트이기에 모듈이 생성되고 초기에 값을 가지고 있어야 하기에

initial 을 사용하여 초기화를 해준다.

그 다음은 counter값이 4가 되게되면 값을 0으로 바꿔주고

out의 값을 반전시키는 코드이다.

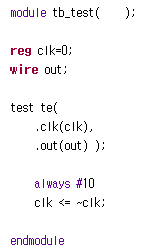

다음은 시뮬레이션 코드이다.

우선 입력신호를 0과 1로 바꿔가며 줄 것이기에

1Bit 크기의 clk신호를 만들어주고 초기화를 진행해준다.

그 다음 out인데 이는 위에서 생성한 모듈의 출력의 출력결과를 연결하여 표현해 줄 것이기에 wire로 생성해주었다.

그리고 이들을 각각 모듈의 clk와 out신호와 맵핑하여주고

테스트벤치의 clk값만을 반복적으로 변화시켜가면서 결과를 확인해본다.

'FPGA > Verilog 공부' 카테고리의 다른 글

| VIVADO 사용법(완전 기초) (2) | 2020.12.29 |

|---|---|

| Verilog를 통한 MUX회로 구현 (0) | 2020.12.29 |

| Verilog를 사용하여 Disparity Map 생성_(1) (0) | 2020.08.28 |

| OV7670 카메라 영상 출력 (0) | 2020.07.28 |

| BRAM (0) | 2020.07.08 |