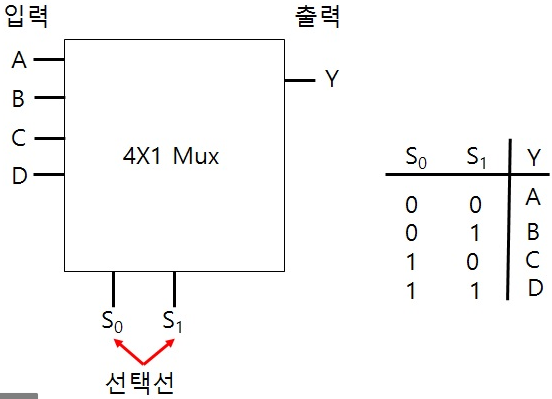

MUX는 다양한 입력신호를 갖고 select 신호에 따라 어떠한 입력을 출력할 것인지 선택하게 된다.

즉 위와 같이 나타낼 수 있으며 S0와 S1의 신호에 따라 어떠한 입력신호를 출력할 것인지 결정하게 된다.

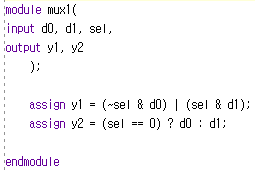

이를 Verilog 코드로 표현하면 아래와 같다.

mux1 이라는 모듈을 만들었는데 입력은 d0, d1의 신호와 어떠한 입력을 출력할 것인지 선택하는 sel 신호가 있다.

출력신호 y1부터 보자.

sel값이 0이면 d1값은 무시되고 ~(sel)을 통해 d0의 값이 출력되게 된다.

반대로 sel값이 1이면 ~(sel)값은 0이 되어 d0가 무시되고 d1의 신호가 출력신호가 된다.

y2는 물음표 기호가 들어가게 된다.

이는 조건에 따른 동작을 선택할 때 사용되고

형식은 다음과 같다.

(판단문) ? [참일 때의 선택] : [거짓일 때의 선택];

즉 위의 예로 보면 sel은 0인가? 참이면 y2는 d0신호, 거짓이면 y2는 d1신호

라는 뜻을 담고 있다.

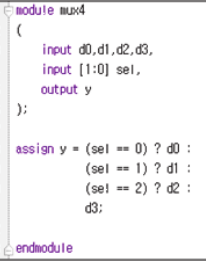

그럼 다음 예제를 보자.

d0부터 d3까지 4개의 입력신호를 갖고 있으므로 4개를 선택할 수 있도록 2bit 크기의 sel 신호가 선언되었다.

하지만 아래 assign의 판단문을 보면 거짓일때의 선택항복이 비어있는 것을 볼 수 있다.

이는 거짓일 경우에 대해서 새로운 조건에 대한 판단을 할 수 있도록 가능성을 열어둔 것이다.

즉 sel이 0인가? 맞다면 d0출력

sel이 0이 아닌가? 그럼 sel이 1인가? 맞다면 d1 출력

이렇게 뒤의 내용들이 이어진 것으로 볼 수 있다.

'FPGA > Verilog 공부' 카테고리의 다른 글

| F/F(플립플롭), Latch(래치), 순차회로, 조합회로 (0) | 2020.12.29 |

|---|---|

| VIVADO 사용법(완전 기초) (2) | 2020.12.29 |

| Verilog를 사용하여 Disparity Map 생성_(1) (0) | 2020.08.28 |

| OV7670 카메라 영상 출력 (0) | 2020.07.28 |

| Verilog를 이용한 Pulse 출력 확인 (0) | 2020.07.19 |