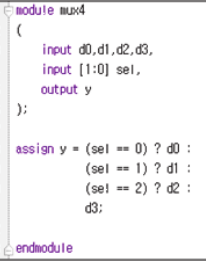

Vivado 첫 화면은 다음과 같다.

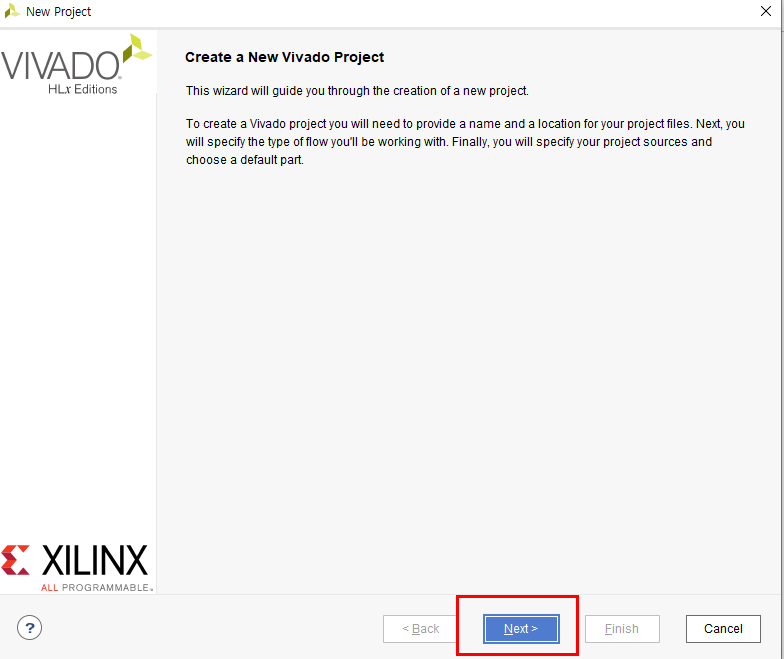

여기서 가장 위의 Create Project를 선택

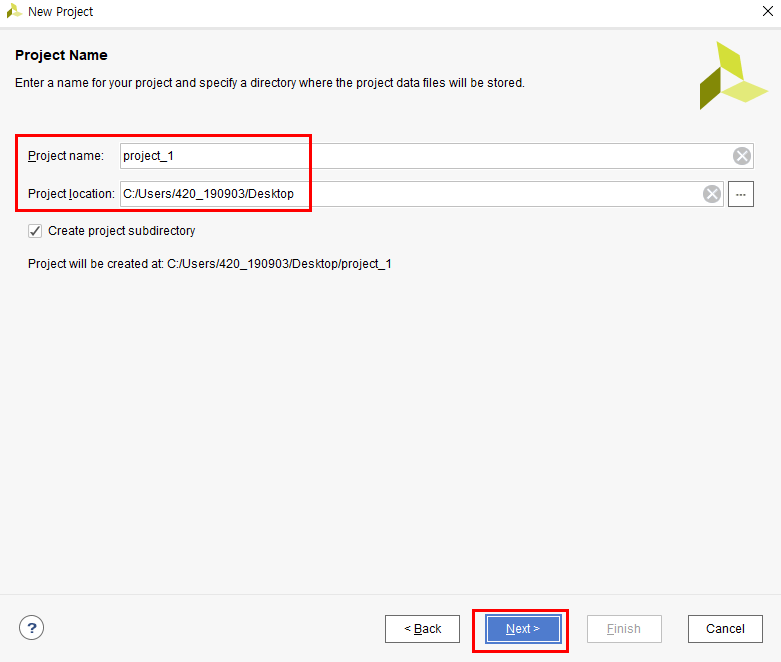

프로젝트 이름과 경로를 설정하고 NEXT

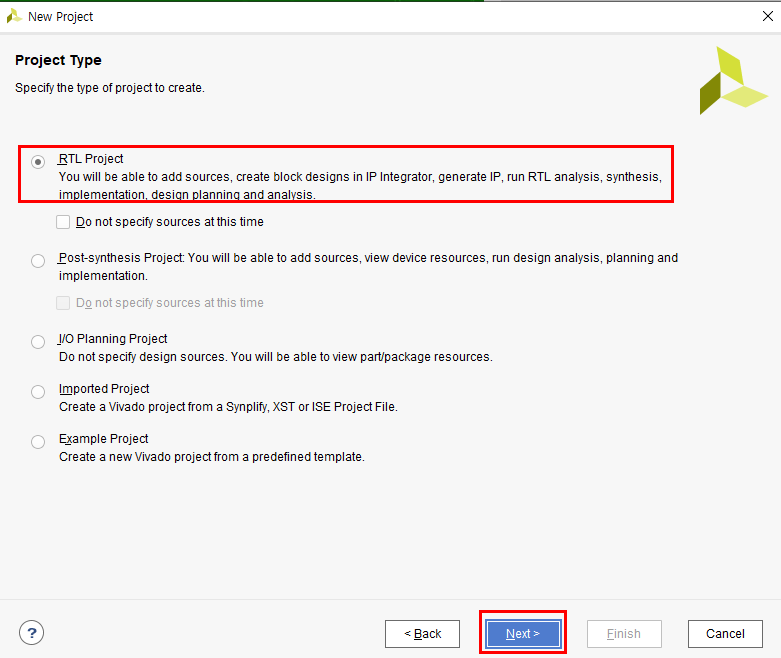

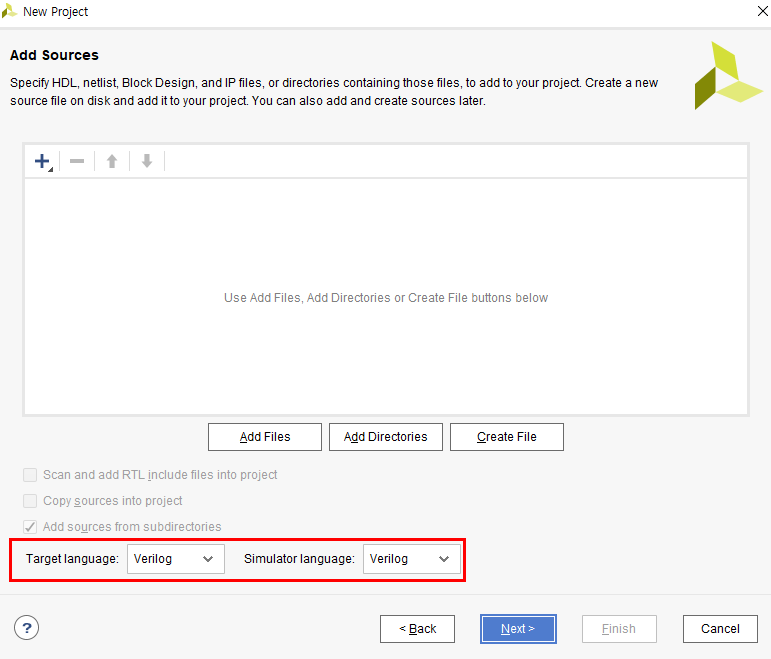

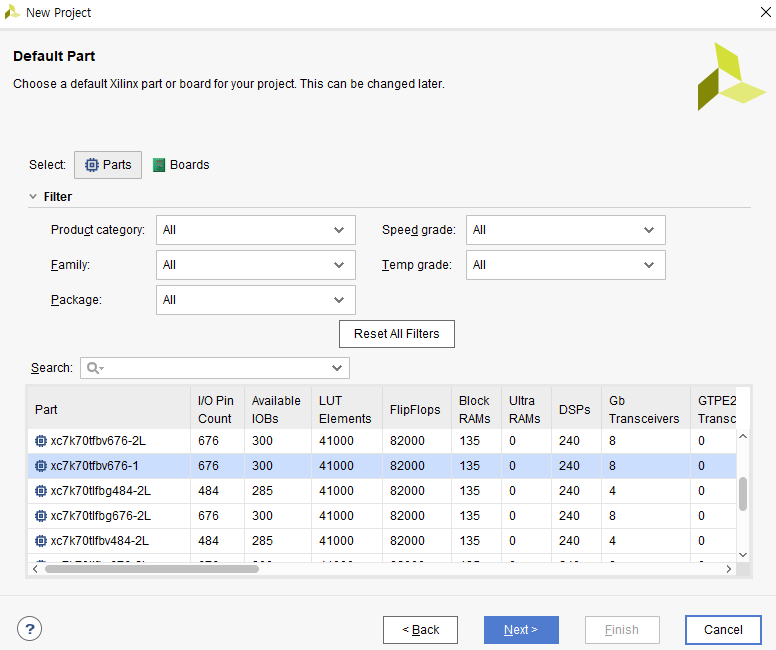

위의 화면에서 일단 나는 장비 없이 간단한 코드들만 실행시켜보면서 시뮬레이션 돌려볼 것이므로

그냥 NEXT를 눌러 진행한다.

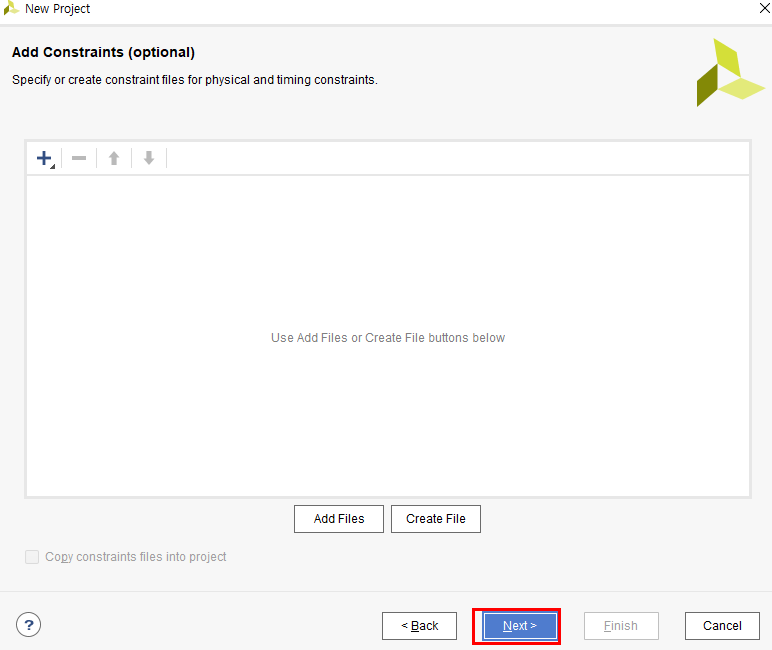

Constraint는 사용할 보드의 구조를 담고있는 파일을 말하는 듯 하다.

이 부분도 현재 보드가 없으므로 그냥 NEXT

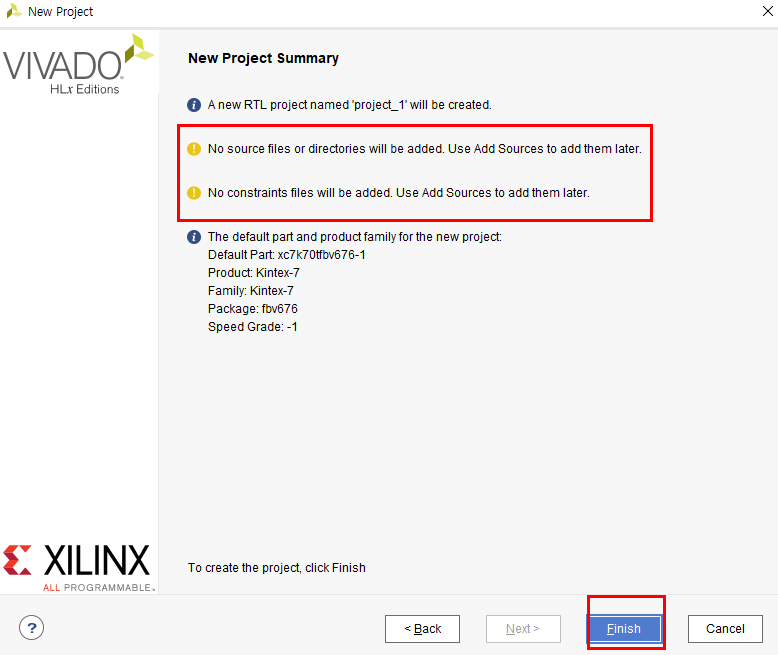

위와 같이 설정 Summery가 확인되는데 source파일을 추가해주지 않았고 constraints 파일을 지정해주지 않았기에

위와 같은 알림이 뜨게 된다.

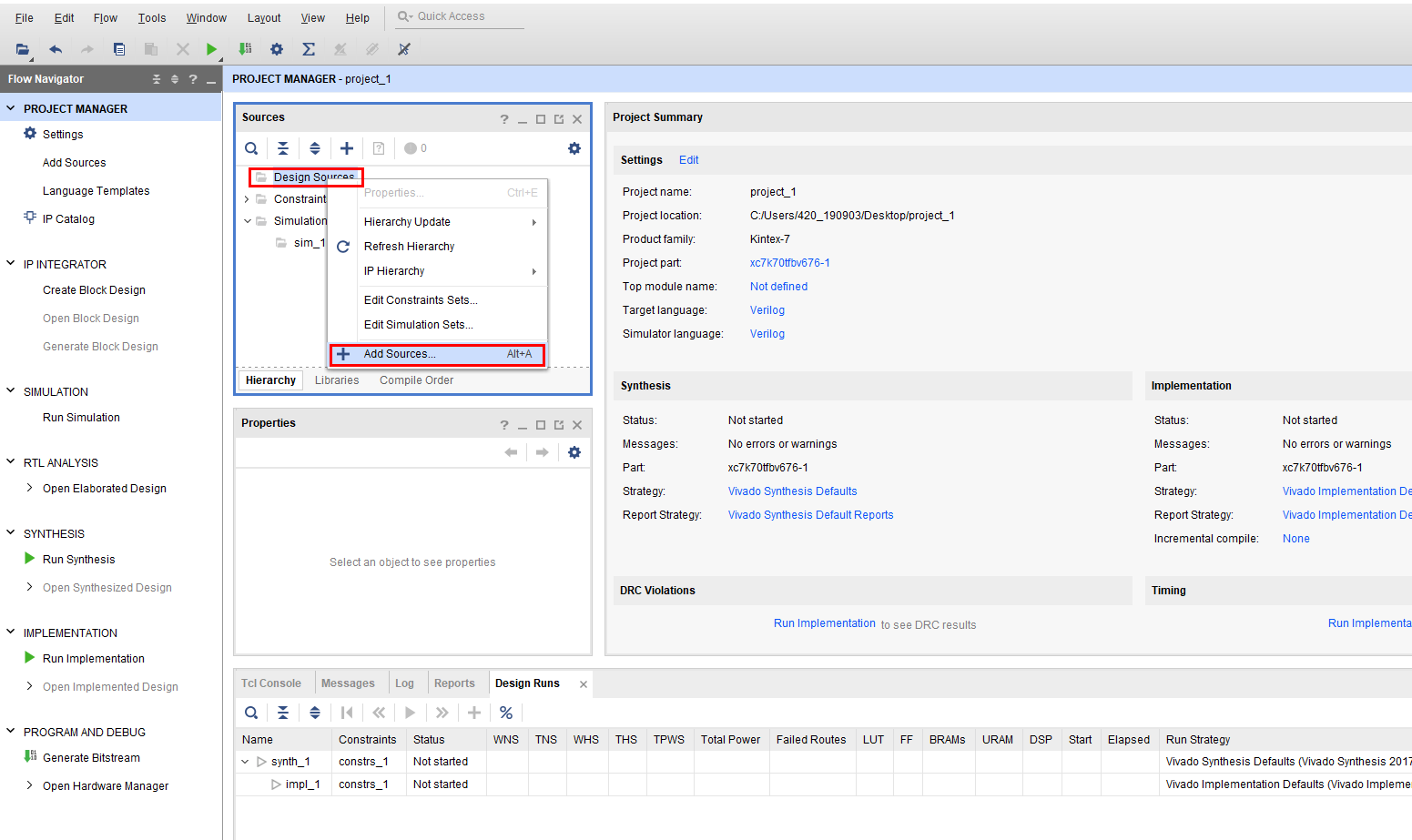

그리고 마무리를 하면 다음과 같은 창이 뜨게된다.

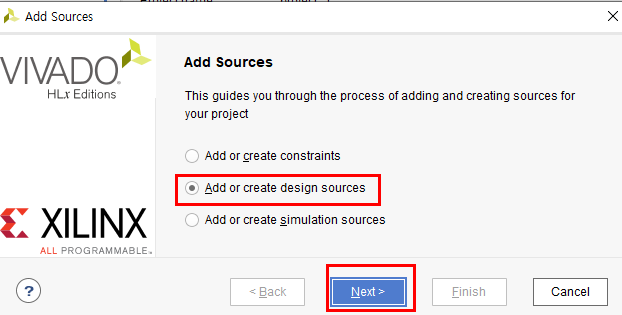

위의 Design Source부분에서 Add Source를 선택하여 소스코드를 넣어주자.

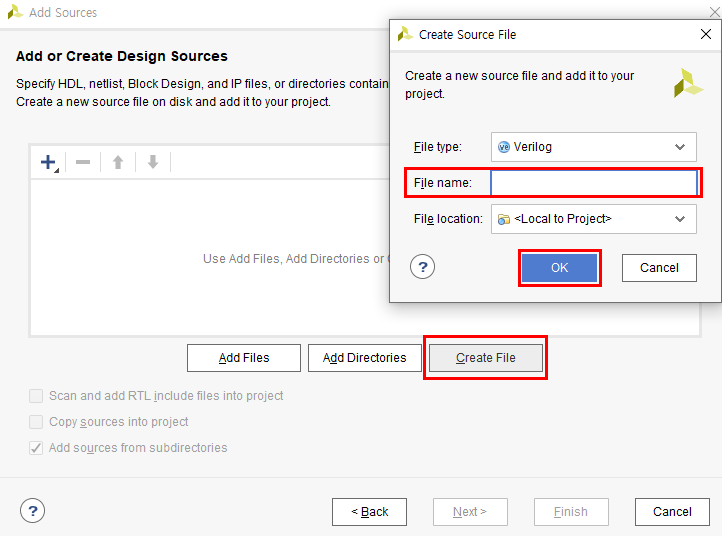

위와 같이 Create File 클릭 수 File name과 File Type을 설정해준다.

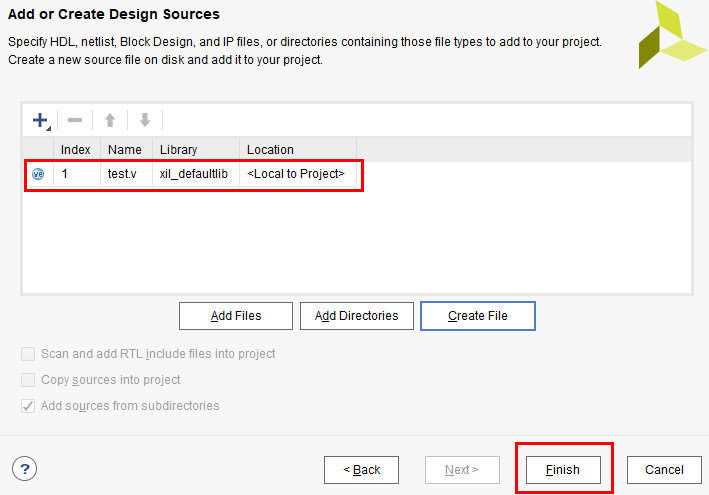

이렇게 test.v 라는 파일이 생성되게 된다.

여기서 test라는 Module의 입출력 포트를 지정해주게 된다.

하지만 나는 여기서 설정하는 것 보다 나중에 코드로 설정하는게 더 편하므로(개인적으로)

여기서는 그냥 OK를 눌러 진행한다.

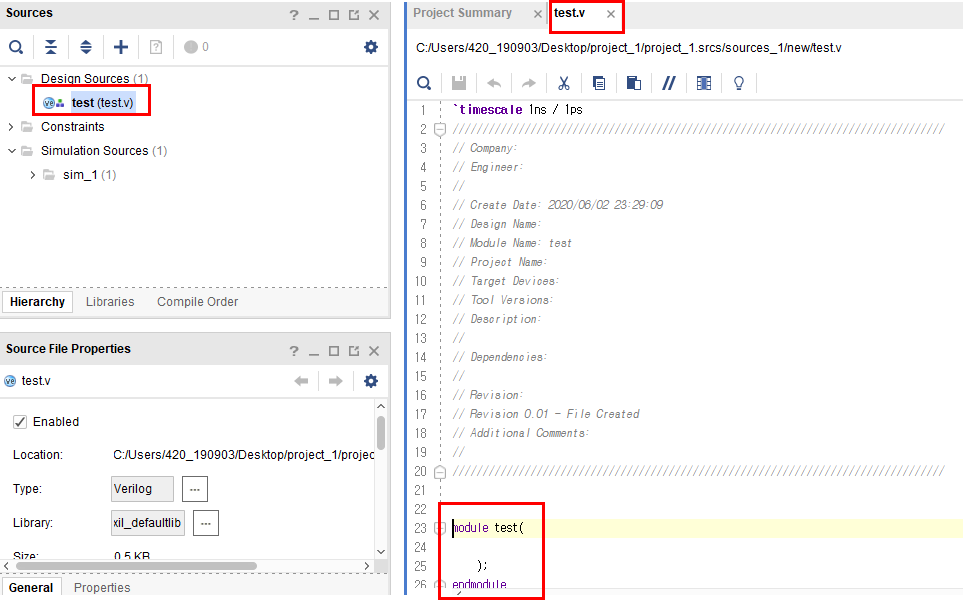

위와 같이 test라는 파일이 만들어지고 또 test라는 모듈이 만들어진 것을 확인할 수 있다.

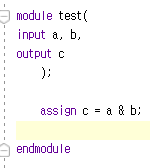

위와 같이 간단한 AND게이트를 만들어보자.

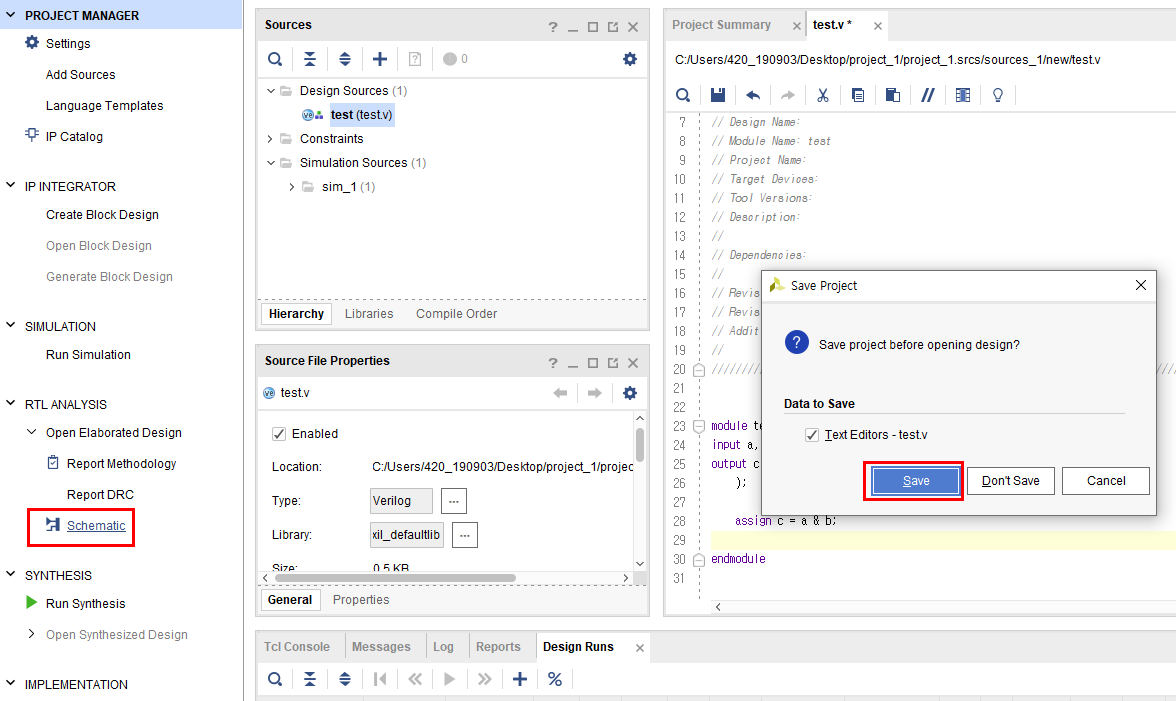

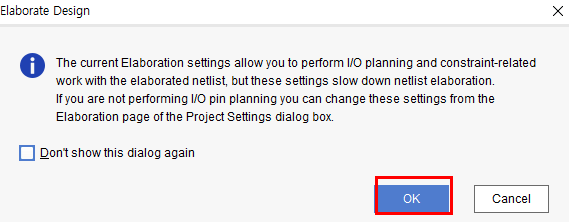

코드로 작성한걸 회로로 보기 위해 좌측 RTL ANALYSIS 항목의 Schematic 선택 후 다음과 같이 진행

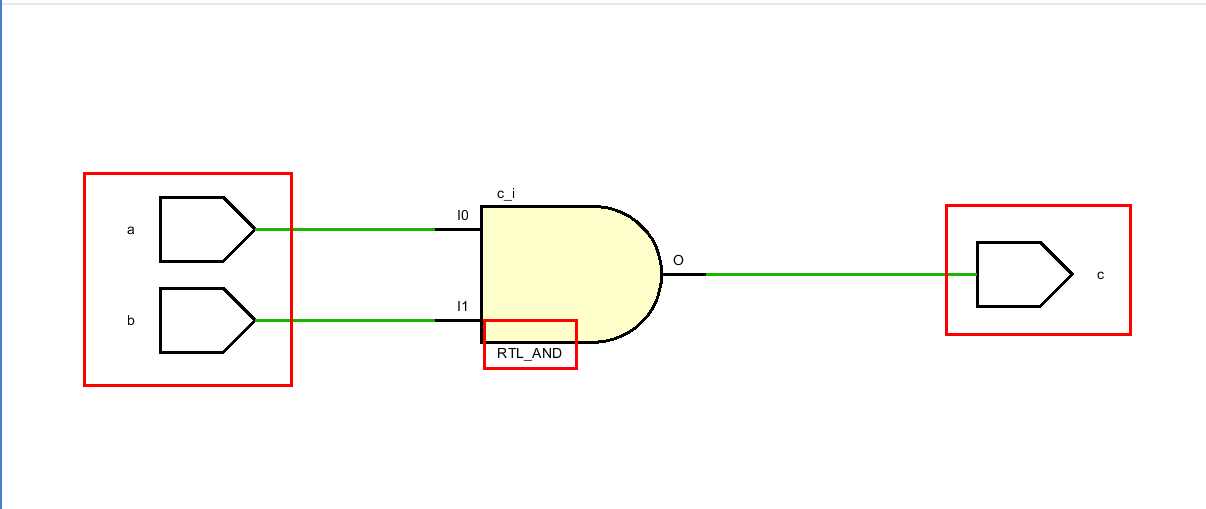

위와 같이 a,b를 입력으로 받고 c를 출력으로 갖는 AND게이트가 나타나게 된다.

그럼 시뮬레이션을 통해 더 작업을 진행해보자.

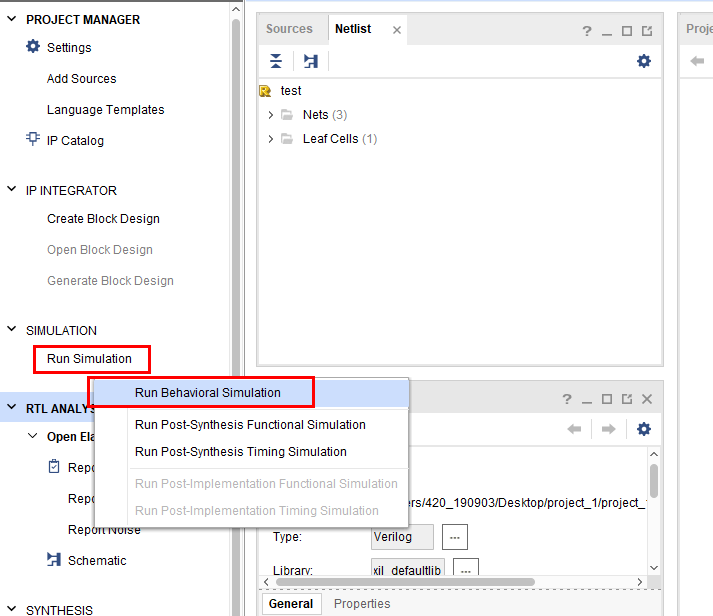

우측의 SIMULATION 항목에서 Run Simulation 진행

그리고 Run Behavioral Simulation 진행

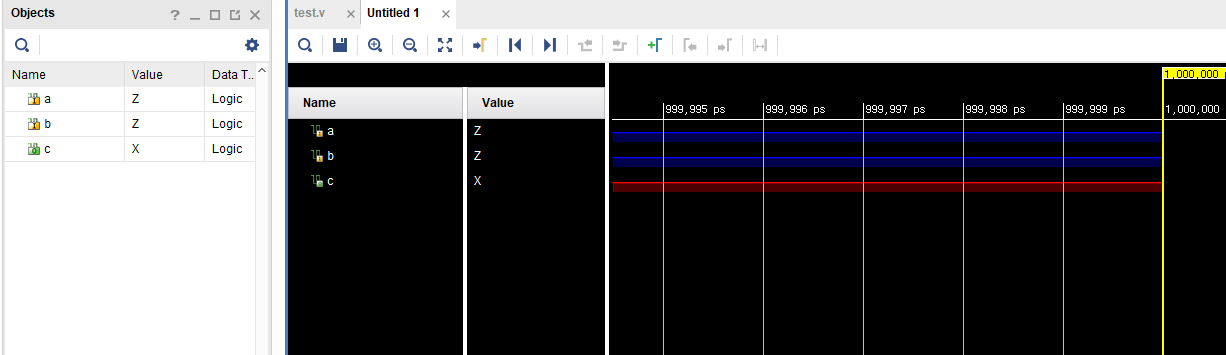

위와 같이 뜨는데 a, b 에 아직 값을 안정해줬기에 Z 라는 이상한 값이 들어가있고

출력을 나타내는 c에도 X 라는 이상한 값이 들어가있다.

그렇기에 입력의 a, b에 값을 넣어줘보자.

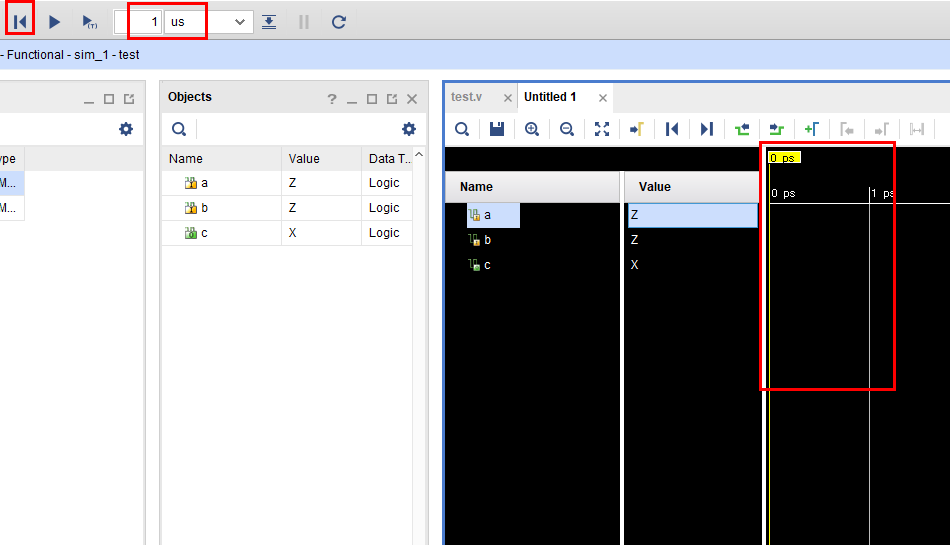

위의 사진에서 가장 좌측 상단의 아이콘을 누르면 시간이 0ps로 이동하는 것을 확인할 수 있다.

그리고 상단의 시간을 표현하는 부분에 1 us 를 선택해주자.

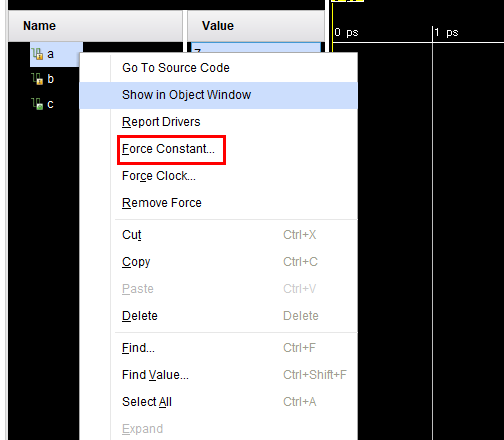

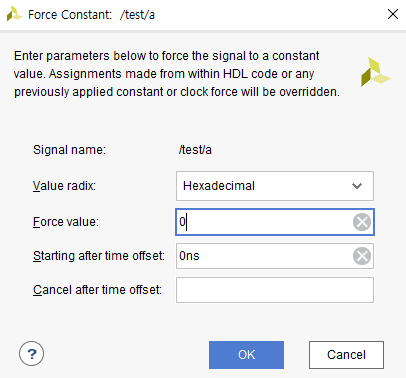

위와 같이 a의 값에 Force Constant를 통해 0이라는 Force Value를 넣어주고 OK

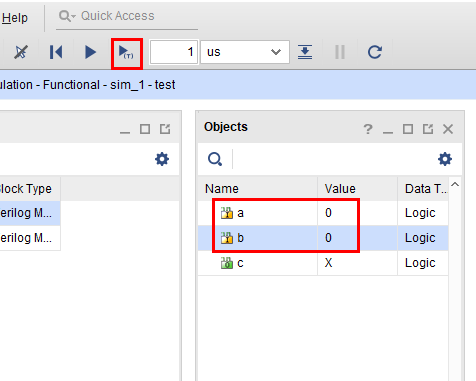

똑같이 b의 값에도 0을 넣어주자.

위와 같이 0이라는 Value가 제대로 들어간 것을 확인할 수 있다.

그럼 상단 시간을 표현하는 부분에 (T)라고 쓰인 아이콘을 클릭

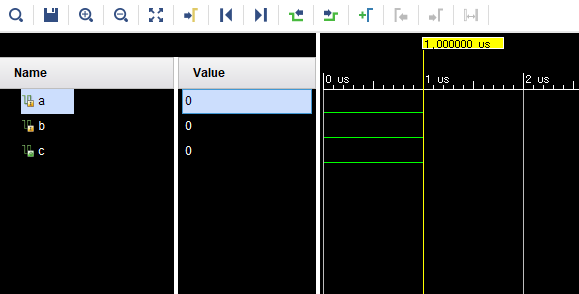

0us부터 시간을 표현하는 부분에 적어준 1us까지 지정해준 값을 통한 출력값 c가 표현된다.

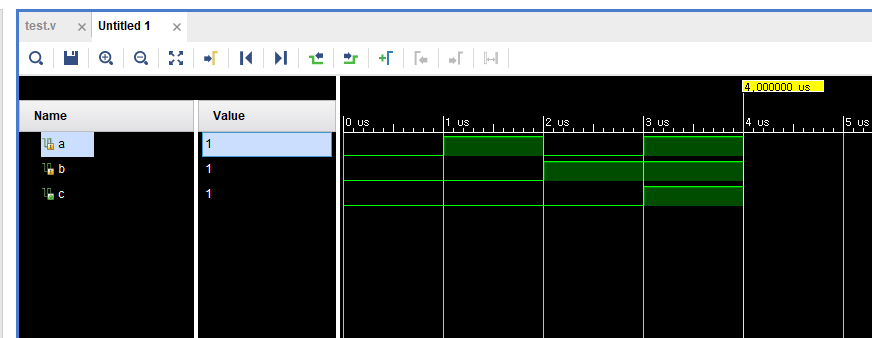

이렇게 진행해보면 입력값에 따른 결과값이 표현되는 것을 확인할 수 있다.

여기까지 완전 기초로 초등학생도 따라할 수 있는 과정이였다.

중간중간 설정이 의미하는게 어떤건지,

좀 더 디테일한 과정을 진행하기 위해선 어떻게 해야하는지

앞으로 차근차근 정리해보겠다.

'FPGA > Verilog 공부' 카테고리의 다른 글

| Verilog 코드를 이용하여 OV7670 카메라모듈 사용하기(SCCB 통신) (1) | 2020.12.29 |

|---|---|

| F/F(플립플롭), Latch(래치), 순차회로, 조합회로 (0) | 2020.12.29 |

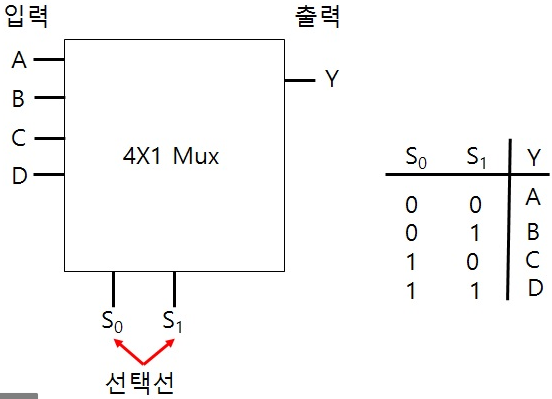

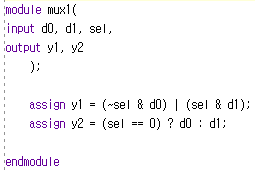

| Verilog를 통한 MUX회로 구현 (0) | 2020.12.29 |

| Verilog를 사용하여 Disparity Map 생성_(1) (0) | 2020.08.28 |

| OV7670 카메라 영상 출력 (0) | 2020.07.28 |