Minized를 사용하여 출력포트를 설정하고

해당 포트로 일정한 pulse가 출력되는 시스템을 구현한다.

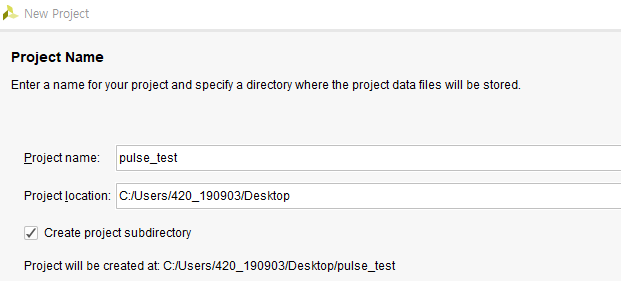

우선 프로젝트를 하나 생성해준다.

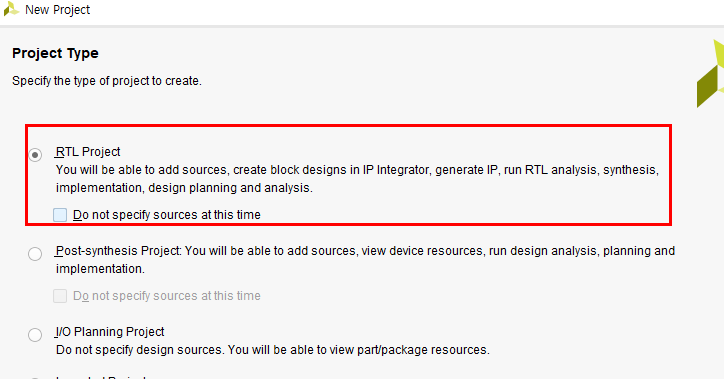

RTL Project로 설정하여 주고

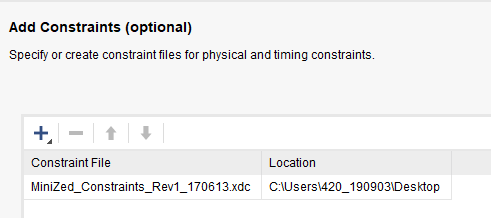

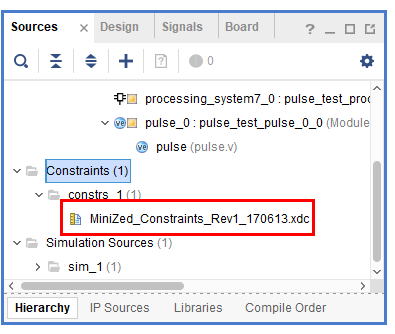

Add Constraints 에서 Minized에 해당되는 .xdc 파일을 선택하여 준다.

해당 파일은 Minized의 각각의 포트들에 대한 정보가 담겨있는 파일이다.

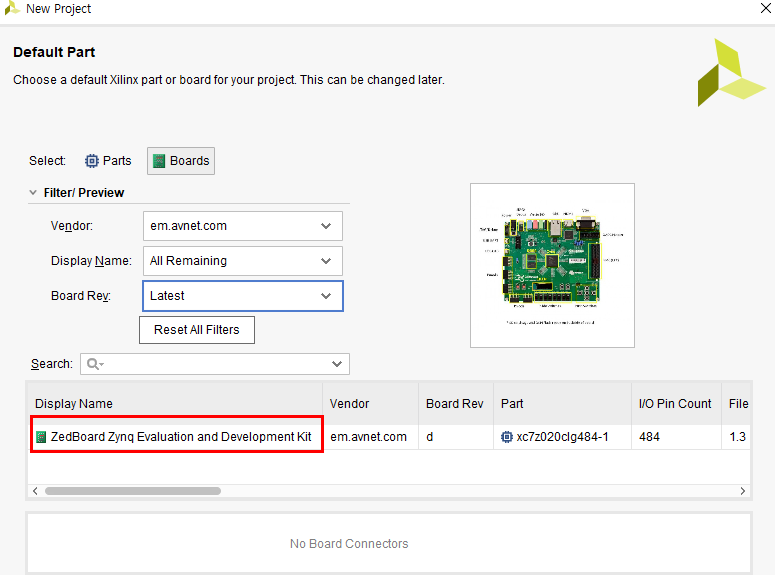

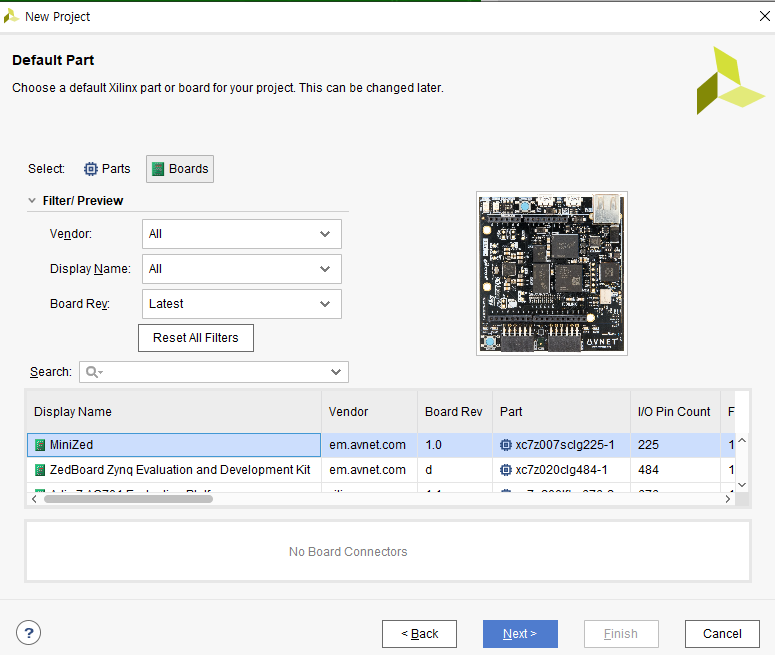

마지막으로 Default Part에서 MiniZed 보드를 선택하여 준다.

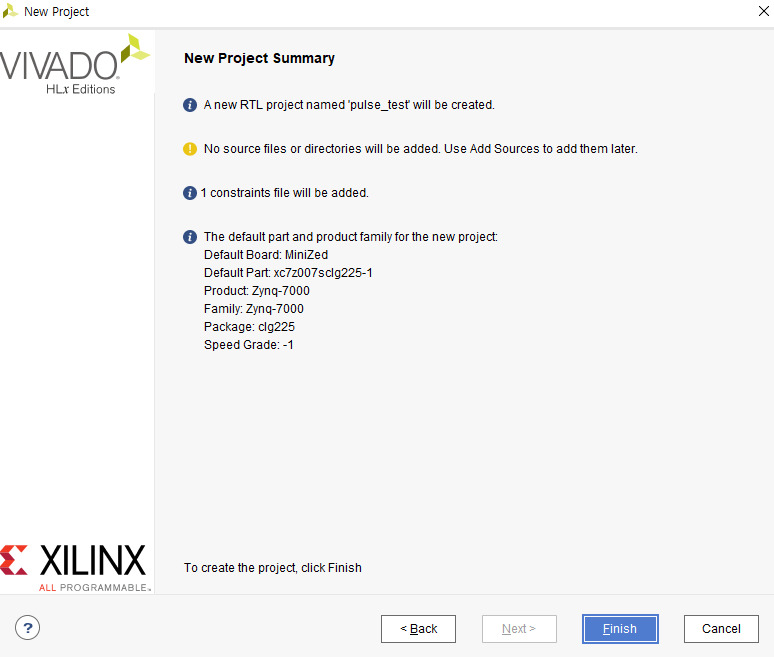

최종적인 프로젝트 환경은 아래와 같다.

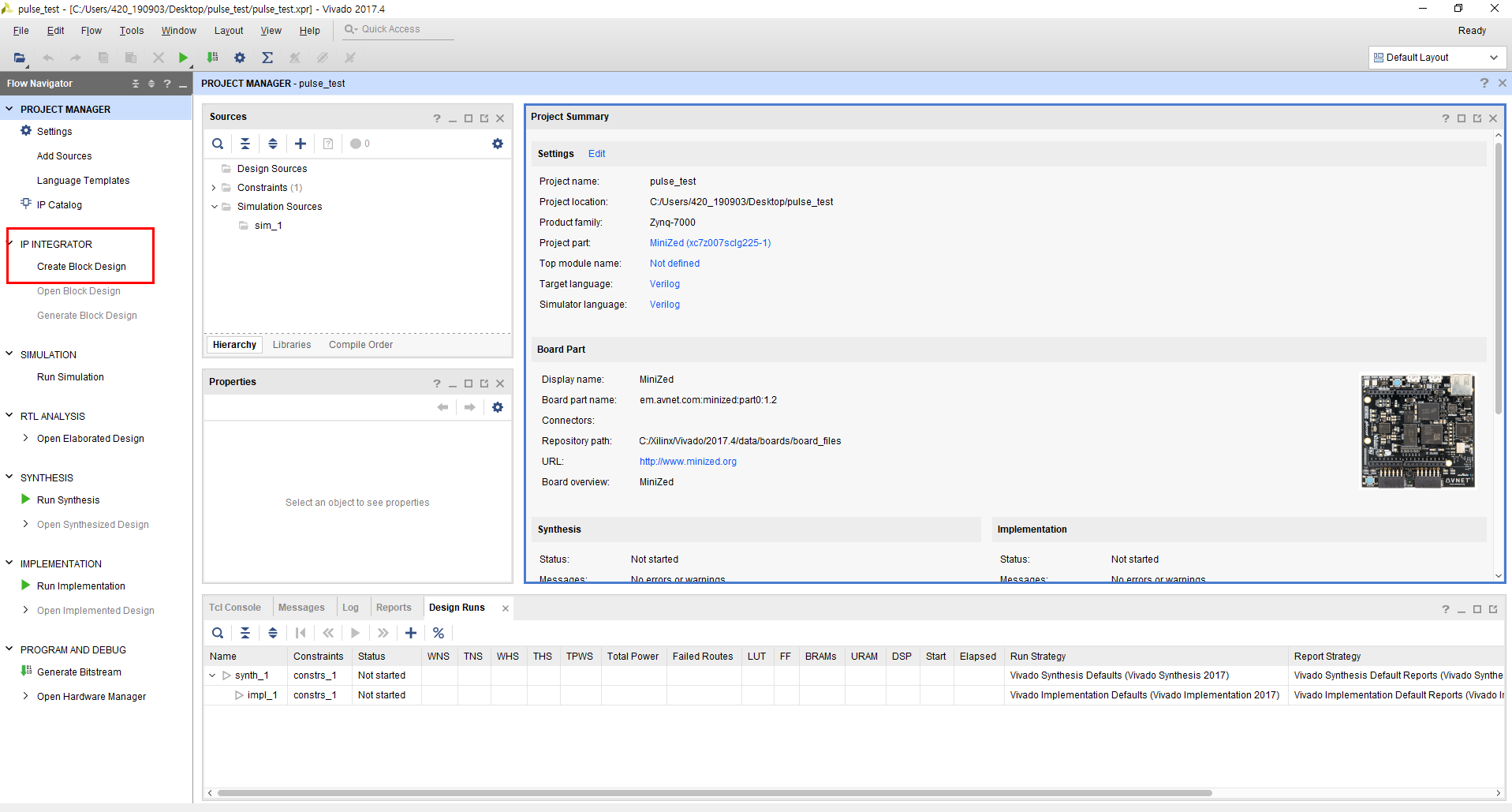

그 후 가장 좌측에 보이는 IP INTEGRATOR 에서 Create Block Design을 선택하여 준다.

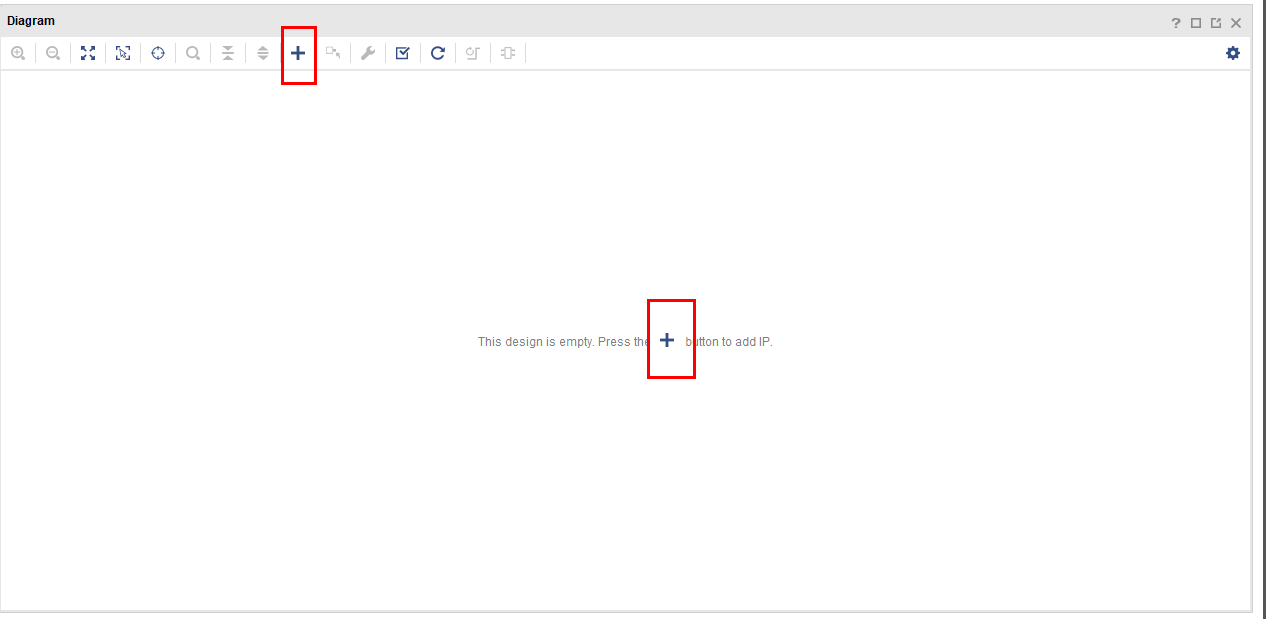

Design Name을 설정하면 아래와 같은 창이 뜨게 되는데 여기서 가운데의 (+) 를 클릭하여 IP를 추가하도록 한다.

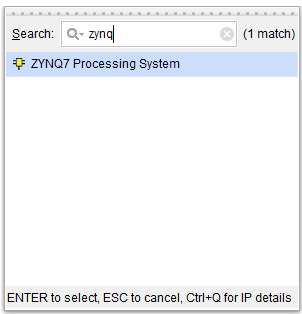

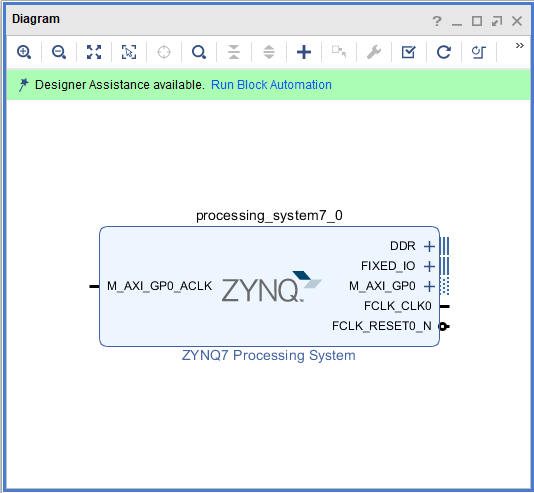

그럼 아래와 같이 검색이 가능한 창이 뜨게 되고 여기서 zync를 입력하여 Zynq7 Proces

sing System IP를 추가하여 준다.

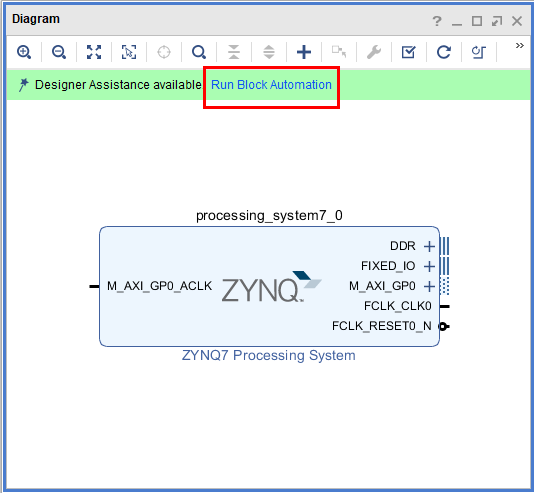

그 후 위의 'Run Block Automation' 을 실행시켜준다.

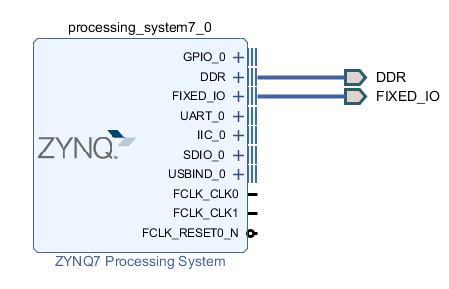

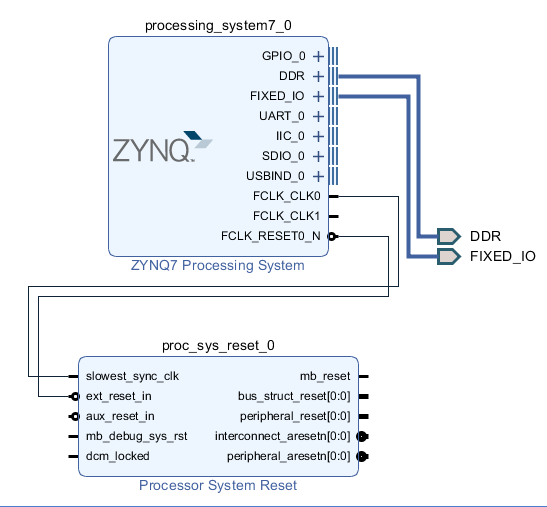

그럼 아래와 같이 포트들이 생성되고

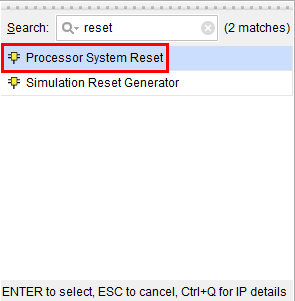

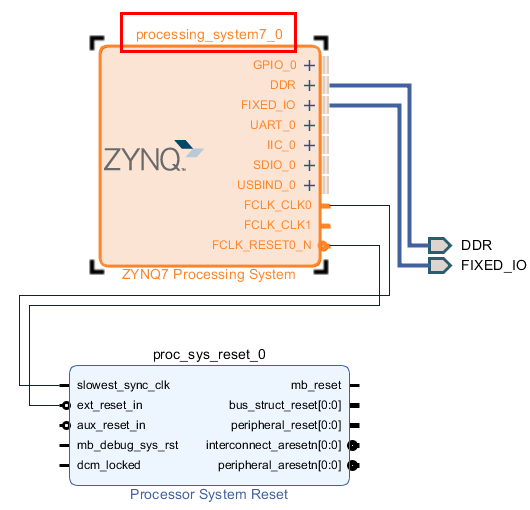

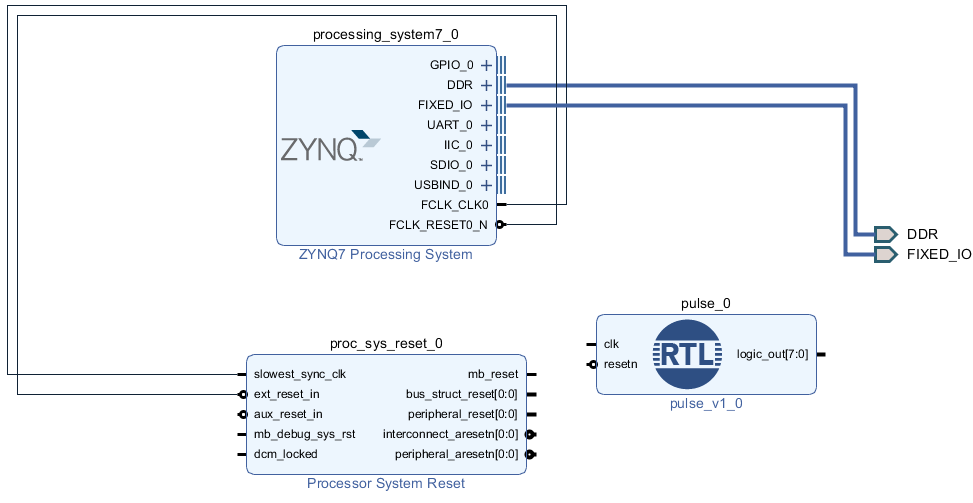

위와 같은 과정으로 Processor System Reset IP를 추가하여준다.

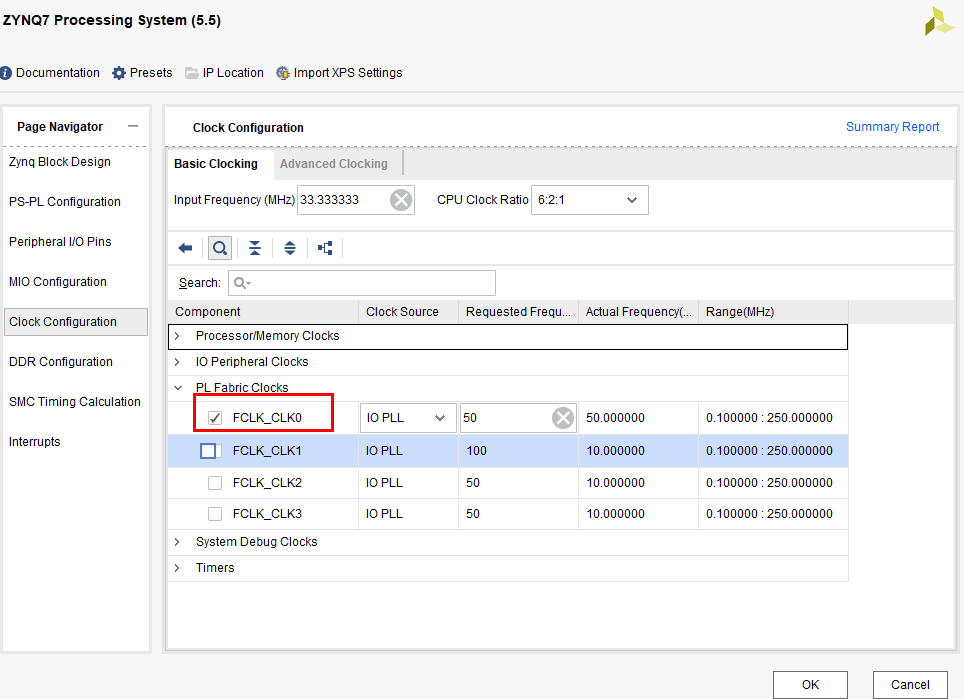

그 다음으로는 클럭을 설정해주어야 한다.

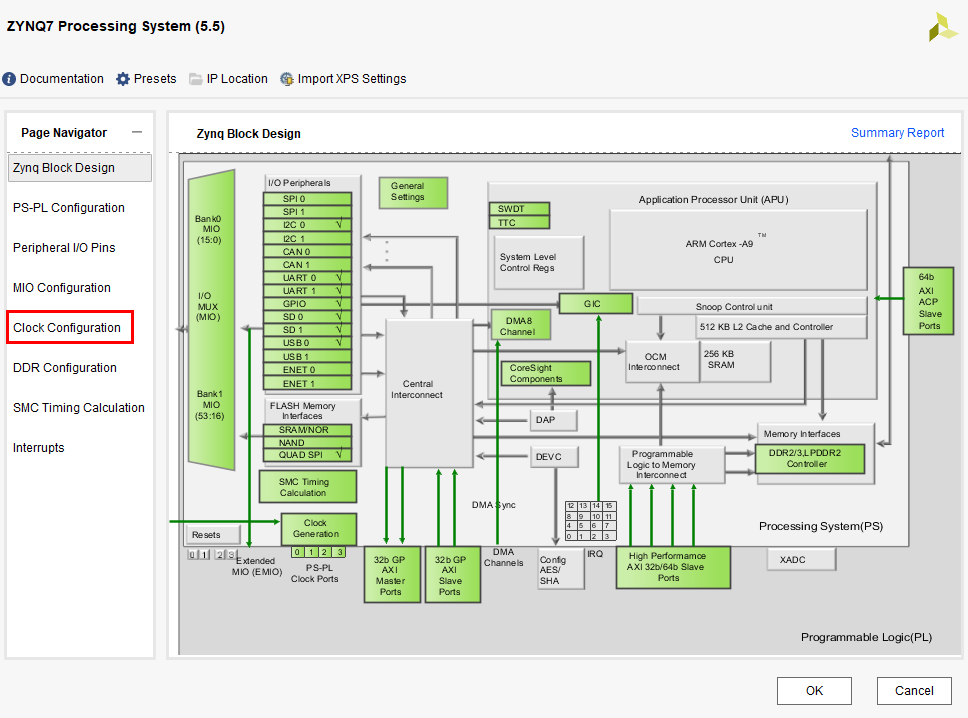

processing_system7_0 을 더블클릭하면 아래와 같은 창이 뜬다.

여기서 Clock Configuration을 클릭해주고

첫번째 체크박스인 FCLK_CLK0 만 체크하여 50MHz의 주파수만을 갖도록 해주자.

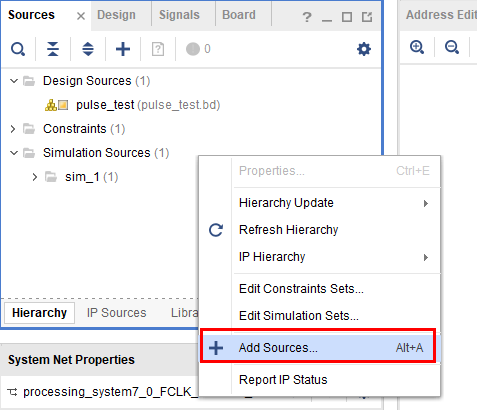

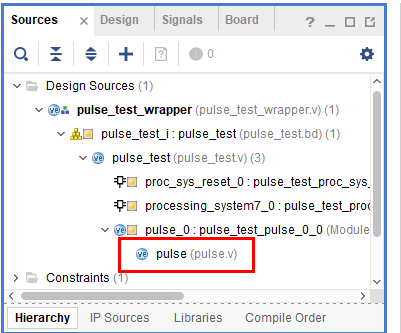

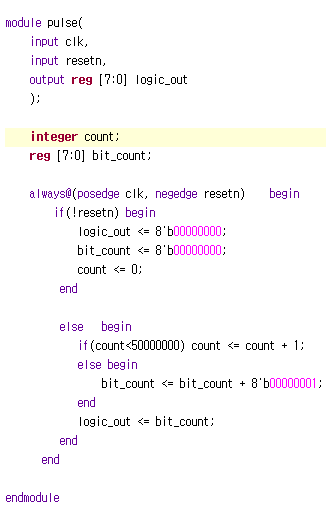

그럼 이제 소스코드를 생성해주자.

Create Design Source

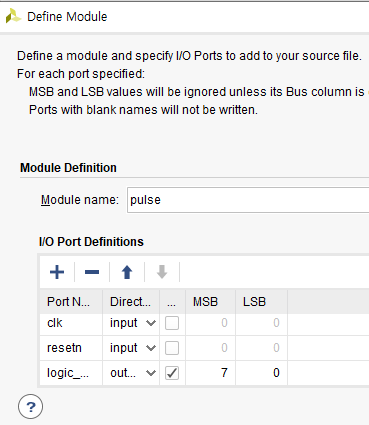

이렇게 모듈을 생성하였으면

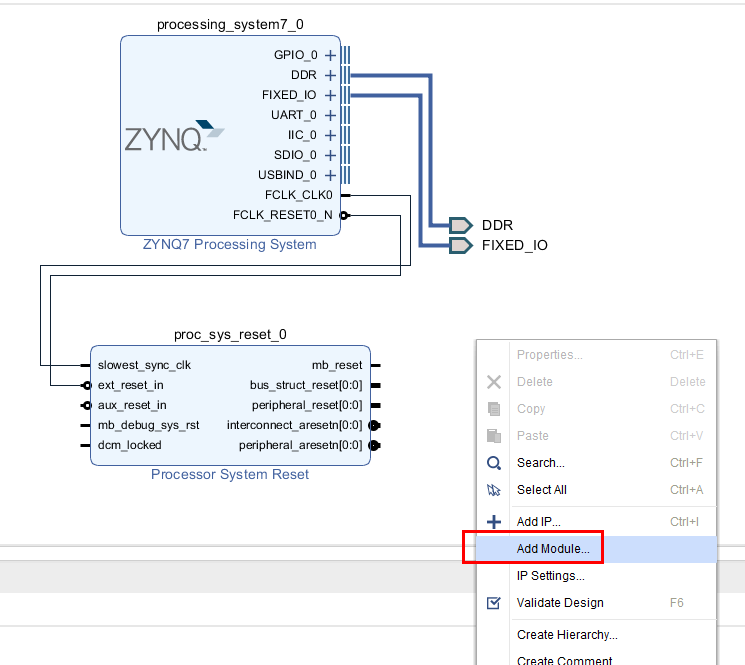

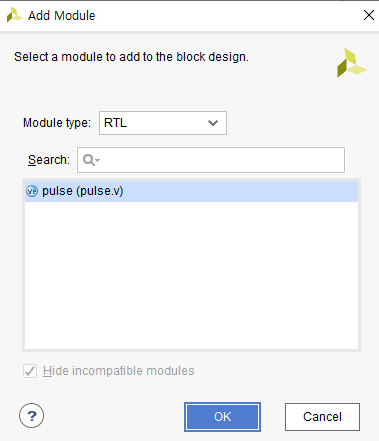

Diagram에서 Add Module을 통해 위에서 소스코드를 통해 만든 모듈을 넣어준다.

소스코드를 만들 때 입출력 포트를 설정해주었으므로 아래와 같이 뜨게 된다.

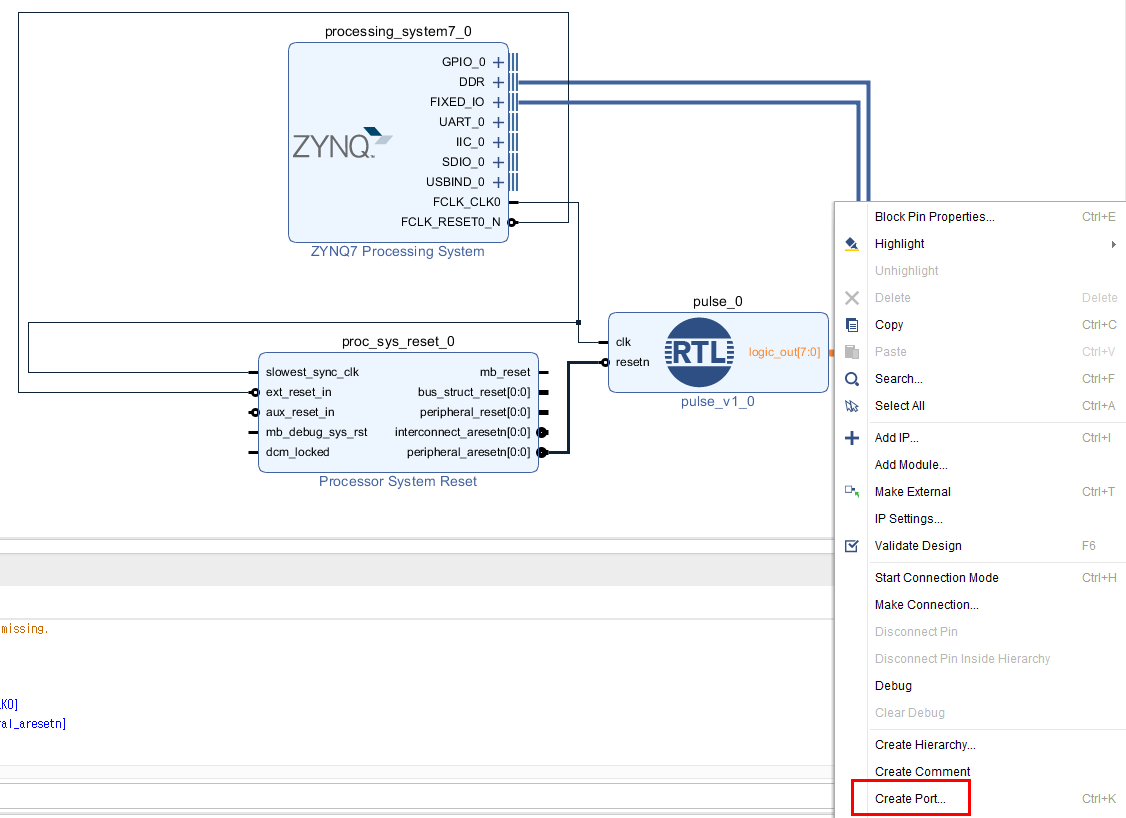

회로는 아래와 같이 설정한 후 logic_out[7:0] 부분을 우클릭 하게 되면 아래와 같이 창이 뜨게 된다.

create port를 선택하여 준다.

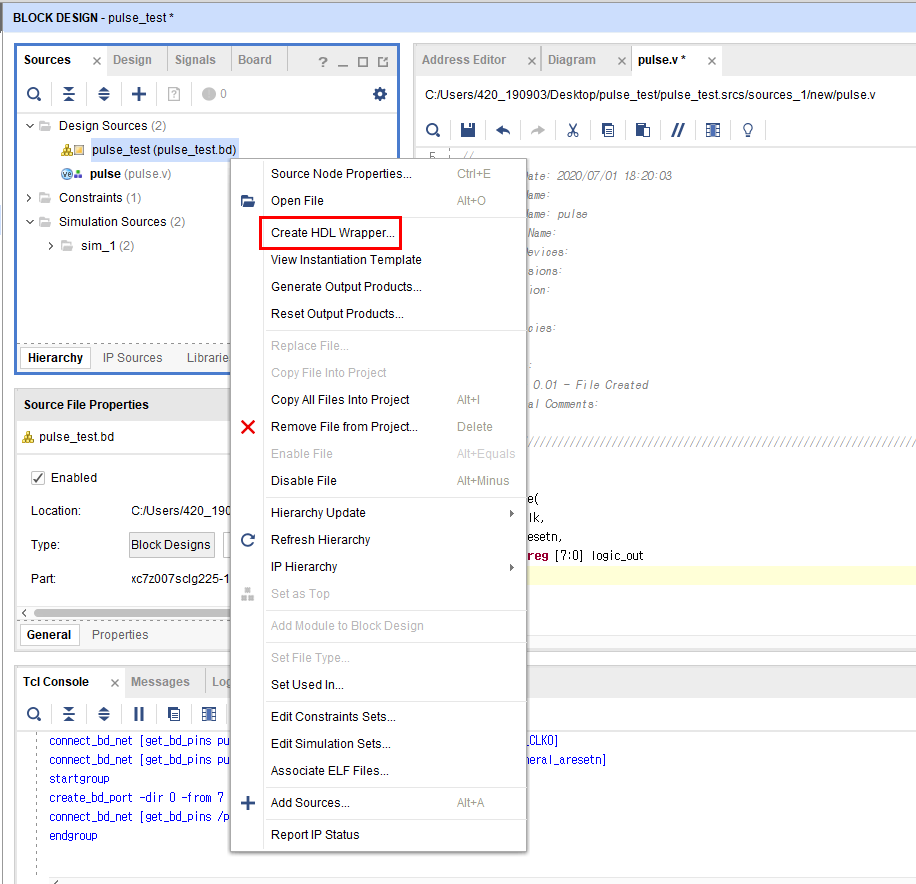

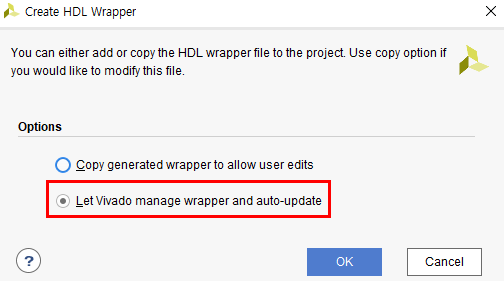

그 다음 Sources 목록의 pulse_test를 우클릭하여 Create HDL Wrapper 을 선택

아래의 창이 뜨면 두번째 항목인 Let Vivado manage wrapper and auto-update를 선택한 후 OK

그럼 이제 아까 만든 모듈의 소스코드로 돌아가 코드를 작성하여 준다.

pulse의 소스코드로 들어가서 아래 내용을 입력해준다

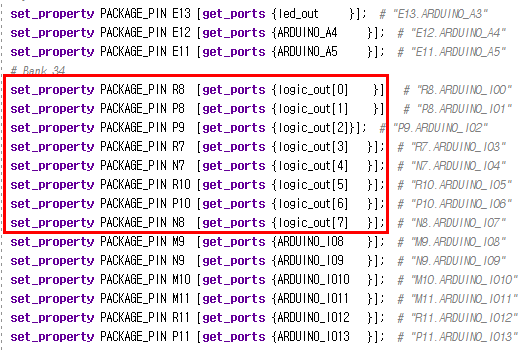

그 후에는 .xdc 파일로 이동하여 Minized의 어떤 포트에서 출력신호를 가질지 정해주면 된다.

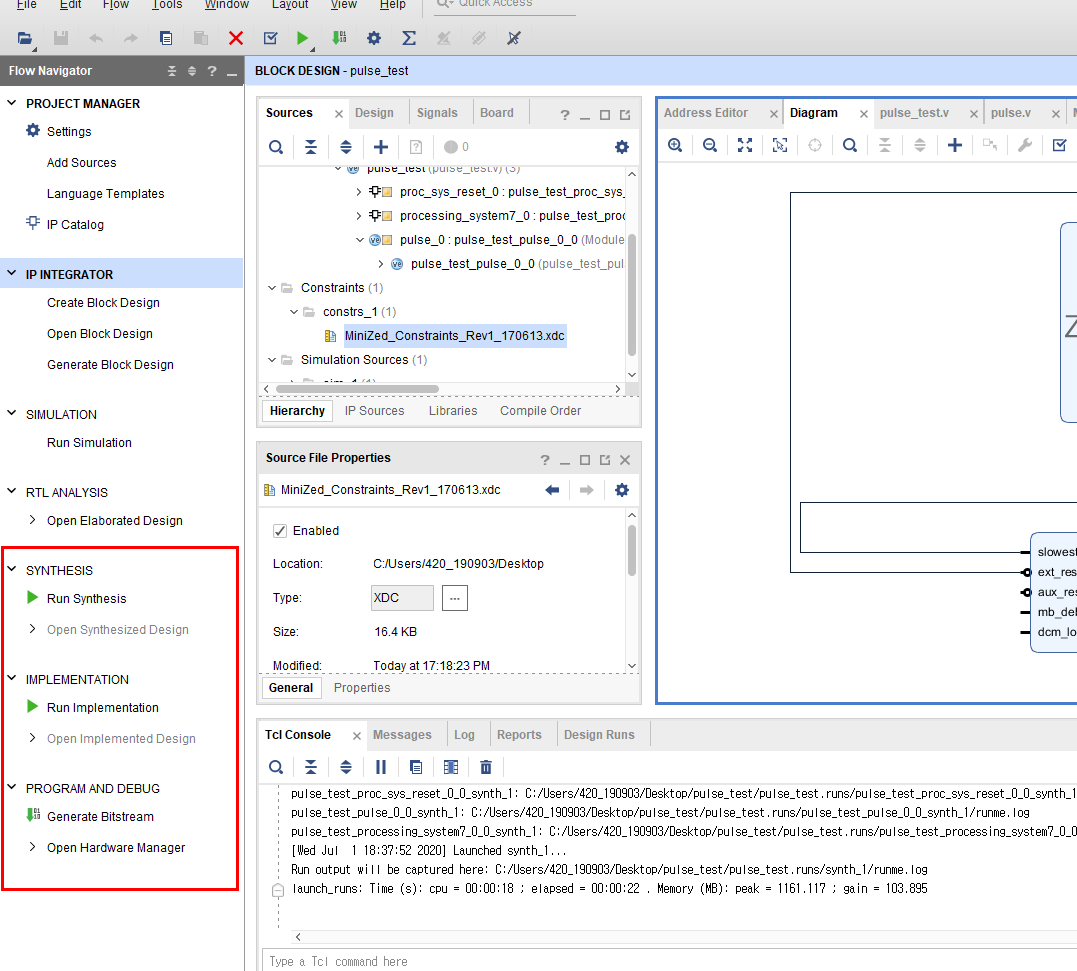

그 다음 Run Synthesis와 Run Implementation, Generate Bitstream을 순차적으로 진행해주면 된다.

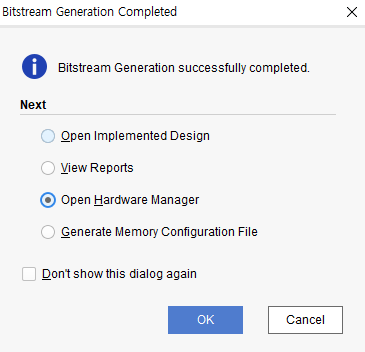

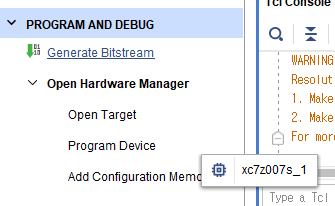

BitstreamGenerator 까지 완료되었으면 Hardware Manager을 실행시킨다.

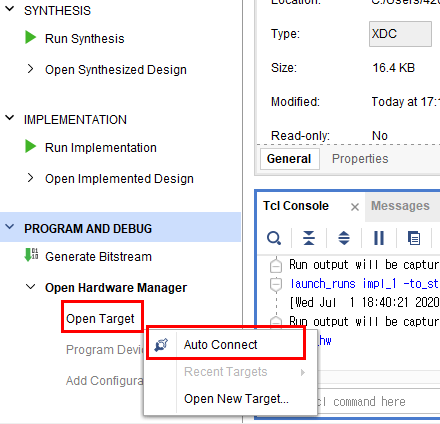

그리고 좌측 항목에서 Open Target, Auto Connect 를 선택

그럼 아래와 같이 내 보드가 뜨는 것을 확인할 수 있고 이를 선택하면

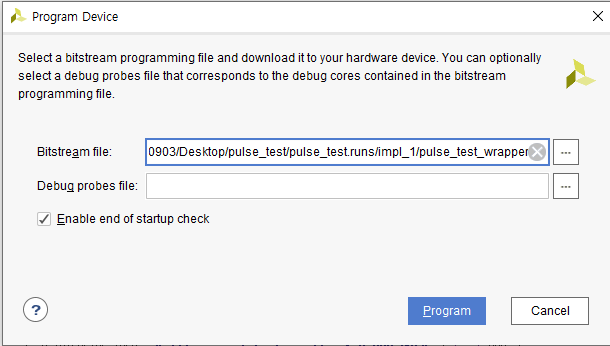

다음과 같이 프로그래밍이 진행되게 된다.

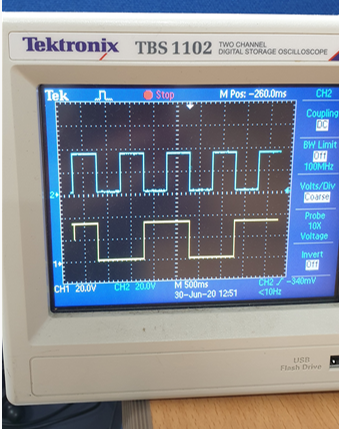

그리고 해당 포트의 출력신호를 확인해보면

위의 사진과 같이 각각 다른 주파수를 갖는 디지털 신호들이 출력됨을 확인할 수 있다.

'FPGA' 카테고리의 다른 글

| Tera Term(테라텀)을 사용하여 FPGA 보드 다루기 (0) | 2020.09.23 |

|---|---|

| MiniZed 를 통한 VGA 출력(Pmod VGA) (0) | 2020.07.02 |

| Minized를 다루기 위한 Vivado 프로젝트 설정 (0) | 2020.06.30 |