Disparity Map을 생성하기 위해 한 쌍의 스테레오 이미지를 불러와 연산을 수행하여야 한다.

해당 스테레오 이미지는 아래의 링크를 통해 다운받았고 혹시 모르니 첨부해놓도록 하겠다.

https://vision.middlebury.edu/stereo/data/scenes2003/

2003 Stereo Datasets

2003 Stereo datasets with ground truth These datasets were created by Daniel Scharstein, Alexander Vandenberg-Rodes, and Rick Szeliski. They consist of high-resolution stereo sequences with complex geometry and pixel-accurate ground-truth disparity data. T

vision.middlebury.edu

Verilog HDL을 통해 이미지파일을 불러오고 Disparity값을 구하여 Depth Map을 생성한 후 결과 파일을 저장하는

과정을 진행하도록 하겠다.

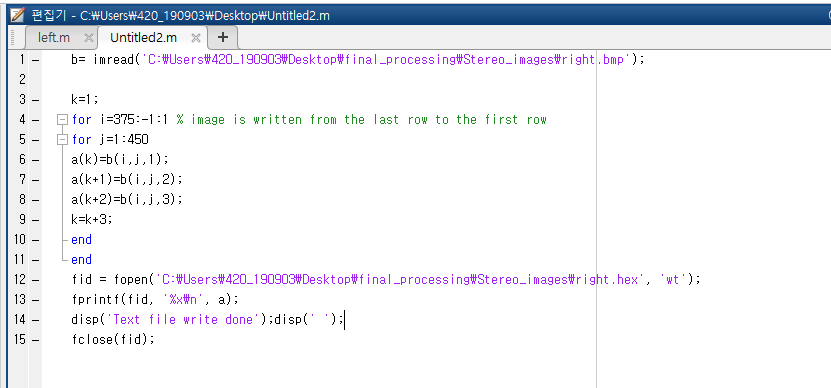

우선 Verilog에서는 이미지파일을 그대로 가져와 연산을 수행하기 힘들기에

Matlab을 통해 .hex파일로 변환해준 후 작업을 진행해야 한다.

Matlab 코드는 위와 같다.

imread를 통해 bmp파일을 불러와 b에 저장하고 해당 값들은 a에 저장된 후

작성되게 된다.

이 과정에서 반복횟수은 375와 450은 각각 이미지파일의 Width와 Height를 의미한다.

위의 과정을 통해 left이미지와 right이미지 파일을 각각 left.hex, right.hex 파일로 변환해주도록 한다.

해당 이미지파일은 Image Rectification과정이 수행된 완전한 수평관계의 이미지들이므로 Rectification과정은 따로

수행하지 않아도 된다.

정확한 3차원 Depth Data를 추출하기 위해선 카메라의 초점거리와 두 카메라 사이의 간격을 알아야 정확한 거리를

계산할 수 있지만 이미지 파일만을 통해선 이러한 스펙들을 알아내기 힘들기에 초점거리와 영상 사이의 거리는 임의로 지정하고 따라서 Depth정보는 정확한 거리가 아닌 상대적인 거리임을 알아두도록 하자.

진행 순서는 아래와 같다.

1. ImageFile을 불러와 Gray_Scale의 데이터로 표현

이 과정에서 1열의 Image File Data를 2차원 배열 크기로 지정해줌으로서 나중에 계산하기 용이하도록 한다.

2. 기준점 지정

이 과정에서는 기준이 되는 좌측 이미지의 어떠한 점(pixel)에 대하여 계산을 진행할 것인지를 지정하게 된다.

입력으로는 CLK신호화 En신호를 두어 En신호가 High상태라면 CLK에 맞추어 Row, Column의 좌표를 출력하고

En신호가 다시 Low를 갖도록 한다.

3. 기준영상의 기준점과 주변 데이터를 1열의 형태로 출력

2단계에서 지점을 정하였으면 해당 지점 주변의 데이터를 출력하도록 한다. 나는 9x9 크기의 윈도우를 생성하여

진행할 것이므로 총 81개의 데이터를 1열로 표현하여 출력하도록 한다.

4. 기준영상의 데이터를 토대로 우측이미지 탐색

앞에서 좌측 이미지의 데이터를 받아온 위치를 알고 있고 Stereo Image는 Rectification이 진행되었으므로 해당 Row

만을 탐색하면 된다. 따라서 우측 이미지의 왼쪽 끝부터 오른쪽 끝까지 해당 Row의 9x9 Window를 생성하고 입력받

은 기준 영상의 데이터와 가장 유사한 점을 선택, 좌측 기준점과 우측 탐색점과의 Disparity값을 출력하도록 한다.

5. 출력된 Disparity값을 통해 거리정보를 계산하고 다시 2단계로 돌아가 그 다음 지점의 기준점에 대해 위의 내용을

반복한다.

'FPGA > Verilog 공부' 카테고리의 다른 글

| VIVADO 사용법(완전 기초) (2) | 2020.12.29 |

|---|---|

| Verilog를 통한 MUX회로 구현 (0) | 2020.12.29 |

| OV7670 카메라 영상 출력 (0) | 2020.07.28 |

| Verilog를 이용한 Pulse 출력 확인 (0) | 2020.07.19 |

| BRAM (0) | 2020.07.08 |